【基础知识】~ FIFO-程序员宅基地

技术标签: fpga开发 IC设计/验证、FPGA

本章目录:

1. 了解FIFO

1.1 定义

FIFO(First In First Out),即先进先出队列。FIFO存储器是一个先入先出的双口缓冲器,即第一个进入其内的数据第一个被移出,其中一个是存储器的输入口,另一个口是存储器的输出口。对于单片FIFO来说,主要有两种结构:触发导向结构和零导向传输结构。触发导向传输结构的FIFO是由寄存器阵列构成的,零导向传输结构的FIFO是由具有读和写地址指针的双口RAM构成。

FPGA 使用的 FIFO 一般指的是对数据的存储具有先进先出特性的一个缓存器,常被用于数据的缓存,或者高速异步数据的交互也即所谓的跨时钟域信号传递。它与 FPGA 内部的 RAM 和 ROM 的区别是没有外部读写地址线,采取顺序写入数据,顺序读出数据的方式,使用起来简单方便,由此带来的缺点就是不能像 RAM 和 ROM 那样可以由地址线决定读取或写入某个指定的地址。

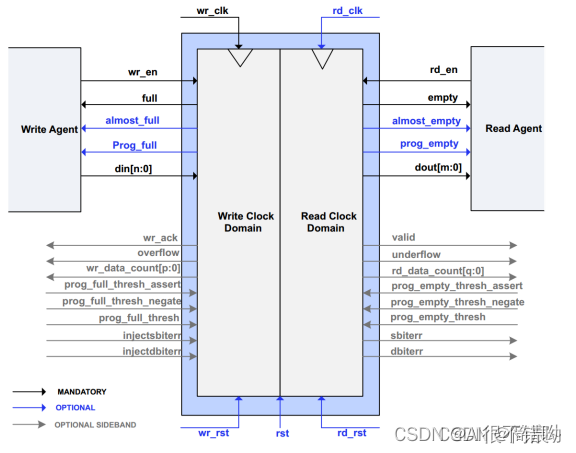

根据 FIFO 工作的时钟域,可以将 FIFO 分为同步 FIFO 和异步 FIFO。同步 FIFO 是指读时钟和写时钟为同一个时钟,在时钟沿来临时同时发生读写操作。异步 FIFO 是指读写时钟不一致,读写时钟是互相独立的。 Xilinx 的 FIFO IP 核可以被配置为同步 FIFO 或异步 FIFO,其信号框图如下图所示。从图中可以了解到,当被配置为同步 FIFO 时,只使用 wr_clk,所有的输入输出信号都同步于 wr_clk 信号。而当被配置为异步 FIFO 时,写端口和读端口分别有独立的时钟,所有与写相关的信号都是同步于写时钟 wr_clk,所有与读相关的信号都是同步于读时钟 rd_clk。

1.2 FIFO有什么用处?

- 跨时钟域

- 在将数据发送到芯片外之前将其缓冲(例如,发送到DRAM或SRAM)

- 缓冲数据以供软件在以后查看

- 存储数据以备后用

1.3 FIFO的参数有哪些?

宽度:一次读写操作的数据位

深度:可以存储的 N 位数据的数目(宽度为 N)

满标志: full。FIFO 已满时,由 FIFO 的状态电路送出的信号,阻止 FIFO 写操作

空标志: empty。FIFO 已空时,由 FIFO 的状态电路送出的信号,阻止 FIFO 读操作

读时钟:读操作所遵循的时钟

写时钟:写操作所遵循的时钟

2. 同步FIFO

2.1 原理

典型同步FIFO由三部分组成:FIFO写控制逻辑、FIFO读控制逻辑、FIFO存储实体。

FIFO写控制逻辑主要功能:产生FIFO写地址、写有效信号,同时产生FIFO写满、写错等状态信号;

FIFO读控制逻辑主要功能:产生FIFO读地址、读有效信号,同时产生FIFO读空、读错等状态信号。

FIFO读写过程的地址控制如下图所示:

当FIFO初始化(复位)时,fifo_write_addr与fifo_read_addr同指到0x0,此时FIFO处于空状态;

当FIFO进行写操作时,fifo_write_addr递增(增加到FIFO DEPTH时回绕),与fifo_read_addr错开,此时FIFO处于非空状态;

当FIFO进行读操作时,fifo_read_addr递增。

FIFO空满状态产生:

为产生FIFO空满标志,引入Count 计数器,用于指示FIFO内部存储数据个数;

当只有写操作时,Count加1;只有读操作时,Count减1;其它情况下,保持不变;

Count为0时,说明FIFO为空,fifo_empty置位;

Count等于FIFO_DEPTH时,说明FIFO已满,fifo_full置位。

2.2 代码

参照博客

3. 异步FIFO

3.1 原理

异步FIFO的实现通常是利用双口RAM和读写地址产生模块来实现的。FIFO的接口包括异步的写时钟(wr_clk)和读时钟(rd_clk)、与写时钟同步的写有效(wr_en)和写数据(wr_data)、与读时钟同步的读有效(rd_en)和读数据(rd_data)。为了实现正确的读写和避免FIFO的上溢或下溢,通常还应该给出与读时钟和写时钟同步的FIFO的空标志(empty)和满标志(full)以禁止读写操作。

写地址产生模块还根据读地址和写地址关系产生FIFO的满标志。当wren有效时,若写地址+2=读地址时,full为1;当wren无效时,若写地址+ 1=读地址时,full为1。读地址产生模块还根据读地址和写地址的差产生FIFO的空标志。当rden有效时,若写地址-1=读地址时,empty为 1;当rden无效时,若写地址=读地址时,empty为1。按照以上方式产生标志信号是为了提前一个时钟周期产生对应的标志信号。

由于空标志和满标志控制了FIFO的操作,因此标志错误会引起操作的错误。如上所述,标志的产生是通过对读写地址的比较产生的,当读写时钟完全异步时,对读写地址进行比较时,可能得出错误的结果。例如,在读地址变化过程中,由于读地址的各位变化并不同步,计算读写地址的差值,可能产生错误的差值,导致产生错误的满标志信号。若将未满标志置为满标志时,可能降低了应用的性能,降低写数据速率;而将满置标志置为未满时,执行一次写操作,则可能产生溢出错误,这对于实际应用来说是绝对应该避免的。空标志信号的产生也可能产生类似的错误。

3.2 最小深度计算

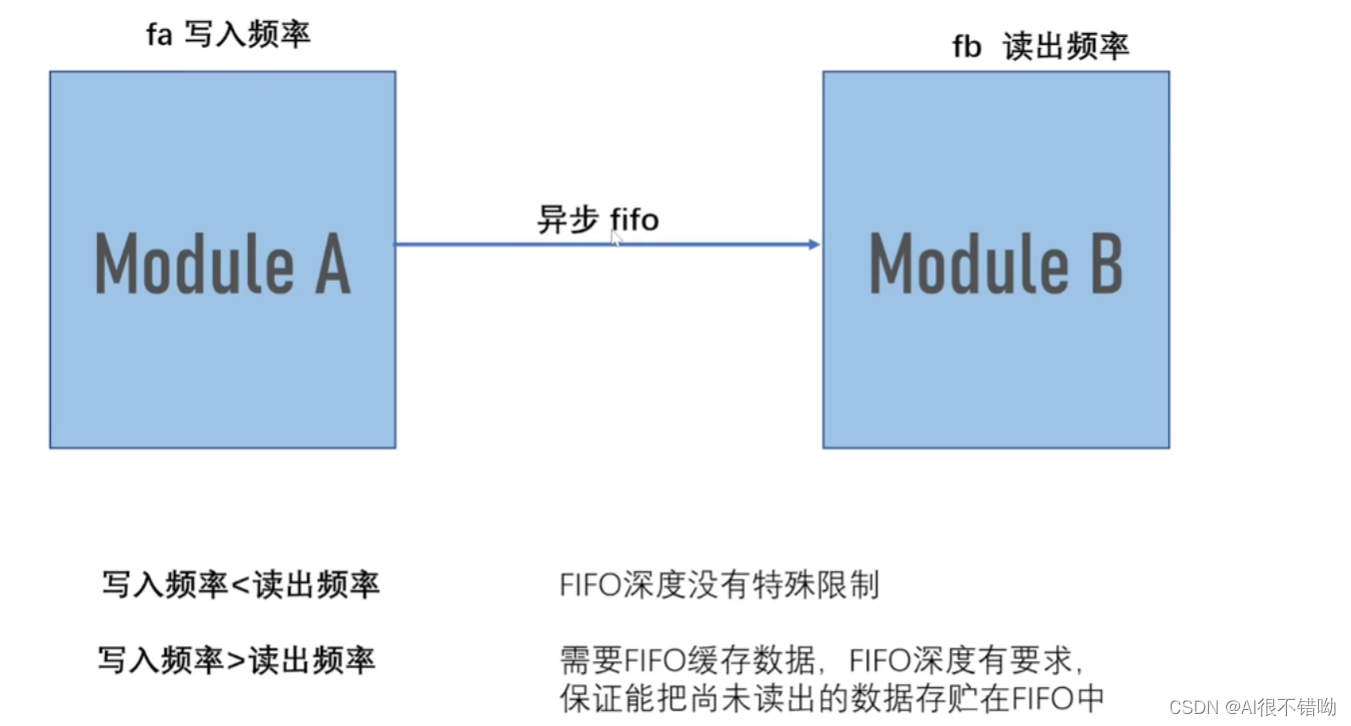

对于异步FIFO而言,无非就是写入频率大于或者小于读出频率呗!然而,对于写入频率 小于 读出频率,意味着写的慢,读的快,会怎样?那肯定是对你的FIFO深度没有要求了呀!你没了我就不读了呗。重要的是看另一种情况:写入大于读出,那就需要FIFO进行储存,既然储存,那肯定得有深度要求!

3.2.1 需要用到FIFO最小深度的情况

大概有以下四种情况:(以上图为例)

- fa>fb并且没有空闲(IDLE)周期;

- fa>fb并且有空闲(IDLE)周期;

- fa<fb并且有空闲(IDLE)周期;

- fa<fb并且随机读写;

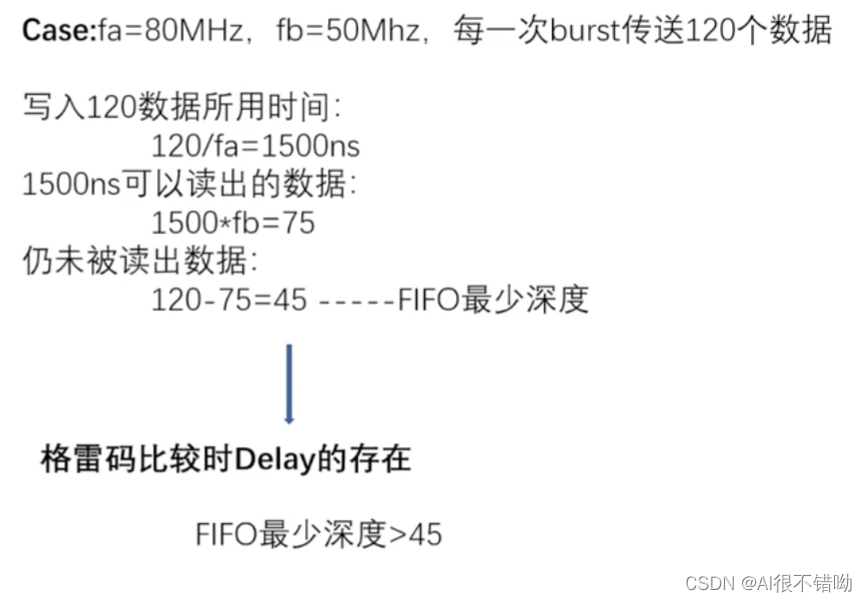

3.2.2 fa>fb并且没有空闲(IDLE)周期

上边这种情况,通过一个例子可以看出来,此时需要FIFO深度。

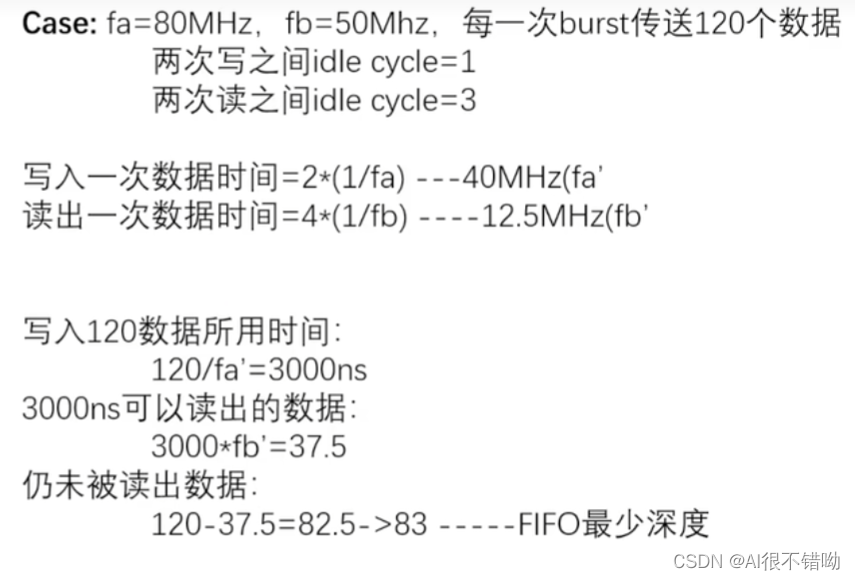

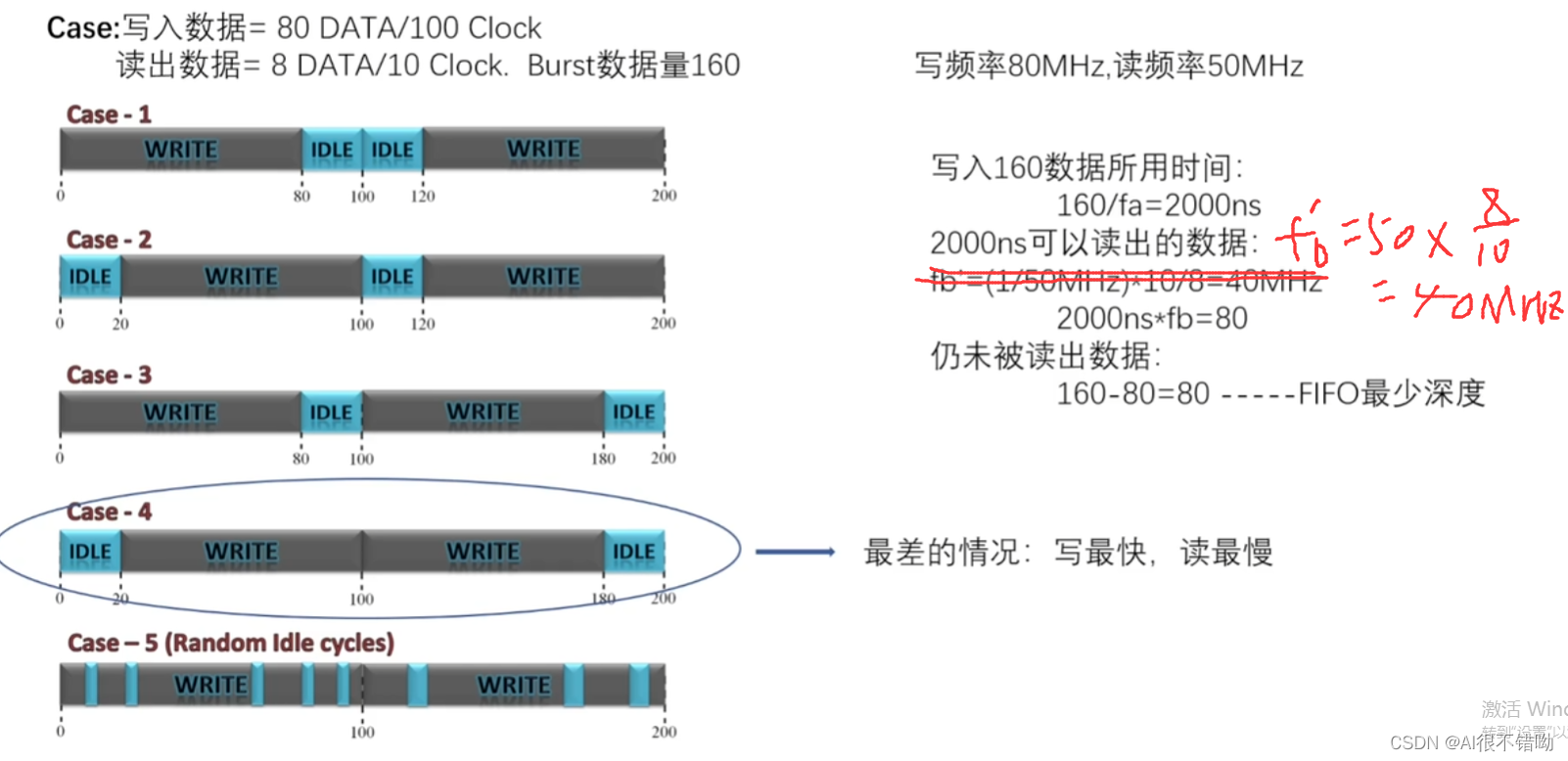

3.2.3 fa>fb并且有空闲(IDLE)周期

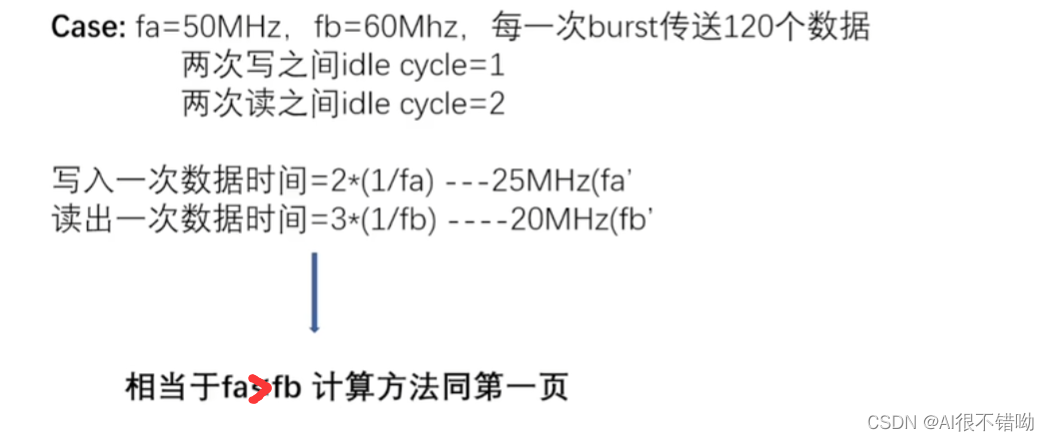

3.2.4 fa<fb并且有空闲(IDLE)周期

3.2.5 fa<fb并且随机读写

通过理解这个例子,我们就可以知道为什么会有下边总结的这些公式了===>

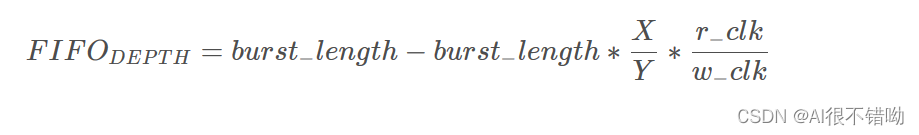

3.2.6 总结最后一种情况的公式

写时钟频率w_clk

读时钟频率 r_clk,

写时钟周期里,每B个时钟周期会有A个数据写入FIFO

读时钟周期里,每Y个时钟周期会有X个数据读出FIFO

举例说明:

假设 FIFO 的写时钟为 100MHZ,读时钟为 80MHZ。在 FIFO 输入侧,每 100 个时钟,写入80 个数据;FIFO 读入测,每个时钟读取一个数据。设计合理的 FIFO 深度,使 FIFO 不会溢出:考虑背靠背(20个clk不发数据+80clk发数据+80clk发数据+20个clk不发数据的200个clk)代入公式可计算FIFO的深度:160-1601(80/100)=32.

3.3 代码实现

参考博客

4. 小试牛刀

基础知识学完之后,那就小试牛刀!

VL22 同步FIFO

代码如下:

`timescale 1ns/1ns

/**********************************RAM************************************/

module dual_port_RAM #(parameter DEPTH = 16,

parameter WIDTH = 8)(

input wclk

,input wenc

,input [$clog2(DEPTH)-1:0] waddr //深度对2取对数,得到地址的位宽。

,input [WIDTH-1:0] wdata //数据写入

,input rclk

,input renc

,input [$clog2(DEPTH)-1:0] raddr //深度对2取对数,得到地址的位宽。

,output reg [WIDTH-1:0] rdata //数据输出

);

reg [WIDTH-1:0] RAM_MEM [0:DEPTH-1];

always @(posedge wclk) begin

if(wenc)

RAM_MEM[waddr] <= wdata;

end

always @(posedge rclk) begin

if(renc)

rdata <= RAM_MEM[raddr];

end

endmodule

/**********************************SFIFO************************************/

module sfifo#(

parameter WIDTH = 8,

parameter DEPTH = 16

)(

input clk ,

input rst_n ,

input winc ,

input rinc ,

input [WIDTH-1:0] wdata ,

output reg wfull ,

output reg rempty ,

output wire [WIDTH-1:0] rdata

);

localparam ADDR_WIDTH = $clog2(DEPTH);

reg [ADDR_WIDTH:0] waddr;

reg [ADDR_WIDTH:0] raddr;

// 写地址 如何操作

always @ (posedge clk or negedge rst_n) begin

if(!rst_n) begin

waddr <= 1'b0;

end

else begin

if(winc && !wfull) begin

waddr <= waddr + 1'b1;

end

else begin

waddr <= waddr;

end

end

end

//读地址 如何操作

always @ (posedge clk or negedge rst_n) begin

if(!rst_n) begin

raddr <= 1'b0;

end

else begin

if(rinc && !rempty) begin

raddr <= raddr + 1'b1;

end

else begin

raddr <= raddr;

end

end

end

//空满判断

always @ (posedge clk or negedge rst_n) begin

if(!rst_n) begin

wfull <= 1'b0;

rempty <= 1'b0;

end

else begin

wfull <= (waddr == {

~raddr[ADDR_WIDTH], raddr[ADDR_WIDTH-1:0]});

rempty <= (raddr == waddr);

end

end

// 实例化

dual_port_RAM #(.DEPTH(DEPTH),

.WIDTH(WIDTH)) dual_port_RAM_0 (.wclk(clk),

.wenc(winc),

.waddr(waddr[ADDR_WIDTH-1:0]),

.wdata(wdata),

.rclk(clk),

.renc(rinc),

.raddr(raddr[ADDR_WIDTH-1:0]),

.rdata(rdata));

endmodule

VL21 异步FIFO

代码如下:

`timescale 1ns/1ns

/***************************************RAM*****************************************/

module dual_port_RAM #(parameter DEPTH = 16,

parameter WIDTH = 8)(

input wclk

,input wenc

,input [$clog2(DEPTH)-1:0] waddr //深度对2取对数,得到地址的位宽。

,input [WIDTH-1:0] wdata //数据写入

,input rclk

,input renc

,input [$clog2(DEPTH)-1:0] raddr //深度对2取对数,得到地址的位宽。

,output reg [WIDTH-1:0] rdata //数据输出

);

reg [WIDTH-1:0] RAM_MEM [0:DEPTH-1];

always @(posedge wclk) begin

if(wenc)

RAM_MEM[waddr] <= wdata;

end

always @(posedge rclk) begin

if(renc)

rdata <= RAM_MEM[raddr];

end

endmodule

/***************************************AFIFO*****************************************/

module asyn_fifo#(

parameter WIDTH = 8,

parameter DEPTH = 16

)(

input wclk ,

input rclk ,

input wrstn ,

input rrstn ,

input winc ,

input rinc ,

input [WIDTH-1:0] wdata ,

output wire wfull ,

output wire rempty ,

output wire [WIDTH-1:0] rdata

);

// 本地参数

localparam ADDR_WIDTH = $clog2(DEPTH);

reg [ADDR_WIDTH:0] waddr;

reg [ADDR_WIDTH:0] raddr;

// 写地址 操作

always @ (posedge wclk or negedge wrstn) begin

if(!wrstn) begin

waddr <= 'b0;

end

else begin

if(winc && !wfull) begin

waddr <= waddr + 1'b1;

end

else begin

waddr <= waddr;

end

end

end

// 读地址 操作

always @ (posedge rclk or negedge rrstn) begin

if(!rrstn) begin

raddr <= 'b0;

end

else begin`timescale 1ns/1ns

/***************************************RAM*****************************************/

module dual_port_RAM #(parameter DEPTH = 16,

parameter WIDTH = 8)(

input wclk

,input wenc

,input [$clog2(DEPTH)-1:0] waddr //深度对2取对数,得到地址的位宽。

,input [WIDTH-1:0] wdata //数据写入

,input rclk

,input renc

,input [$clog2(DEPTH)-1:0] raddr //深度对2取对数,得到地址的位宽。

,output reg [WIDTH-1:0] rdata //数据输出

);

reg [WIDTH-1:0] RAM_MEM [0:DEPTH-1];

always @(posedge wclk) begin

if(wenc)

RAM_MEM[waddr] <= wdata;

end

always @(posedge rclk) begin

if(renc)

rdata <= RAM_MEM[raddr];

end

endmodule

/***************************************AFIFO*****************************************/

module asyn_fifo#(

parameter WIDTH = 8,

parameter DEPTH = 16

)(

input wclk ,

input rclk ,

input wrstn ,

input rrstn ,

input winc ,

input rinc ,

input [WIDTH-1:0] wdata ,

output wire wfull ,

output wire rempty ,

output wire [WIDTH-1:0] rdata

);

// 本地参数

localparam ADDR_WIDTH = $clog2(DEPTH);

reg [ADDR_WIDTH:0] waddr;

reg [ADDR_WIDTH:0] raddr;

// 写地址 操作

always @ (posedge wclk or negedge wrstn) begin

if(~wrstn) begin

waddr <= 'b0;

end

else begin

if(winc && ~wfull) begin

waddr <= waddr + 1'b1;

end

else begin

waddr <= waddr;

end

end

end

// 读地址 操作

always @ (posedge rclk or negedge rrstn) begin

if(~rrstn) begin

raddr <= 'b0;

end

else begin

if(rinc && ~rempty) begin

raddr <= raddr + 1'b1;

end

else begin

raddr <= raddr;

end

end

end

// 二进制 转 格雷码

wire [ADDR_WIDTH:0] waddr_gray;

wire [ADDR_WIDTH:0] raddr_gray;

assign waddr_gray = waddr ^ (waddr>>1);

assign raddr_gray = raddr ^ (raddr>>1);

// 因为上边转码的时候是 组合逻辑赋值,为了避免出现亚稳态,这里打一拍

reg [ADDR_WIDTH:0] waddr_gray_reg;

always @ (posedge wclk or negedge wrstn) begin

if(~wrstn) begin

waddr_gray_reg <= 'd0;

end

else begin

waddr_gray_reg <= waddr_gray;

end

end

//因为上边转码的时候是 组合逻辑赋值,为了避免出现亚稳态,这里打一拍

reg [ADDR_WIDTH:0] raddr_gray_reg;

always @ (posedge rclk or negedge rrstn) begin

if(~rrstn) begin

raddr_gray_reg <= 'd0;

end

else begin

raddr_gray_reg <= raddr_gray;

end

end

// 读时钟域 同步到 写时钟域 ===> 跨时钟域,打两拍

reg [ADDR_WIDTH:0] addr_r2w_temp;

reg [ADDR_WIDTH:0] addr_r2w;

always @ (posedge wclk or negedge wrstn) begin

if(~wrstn) begin

addr_r2w_temp <= 'd0;

addr_r2w <= 'd0;

end

else begin

addr_r2w_temp <= raddr_gray_reg;

addr_r2w <= addr_r2w_temp;

end

end

// 写时钟域 同步到 读时钟域 ===> 跨时钟域,打两拍

reg [ADDR_WIDTH:0] addr_w2r_temp;

reg [ADDR_WIDTH:0] addr_w2r;

always @ (posedge rclk or negedge rrstn) begin

if(~rrstn) begin

addr_w2r_temp <= 'd0;

addr_w2r <= 'd0;

end

else begin

addr_w2r_temp <= waddr_gray_reg;

addr_w2r <= addr_w2r_temp;

end

end

// 空满判断

assign wfull = (waddr_gray_reg == {

~addr_r2w[ADDR_WIDTH:ADDR_WIDTH-1], addr_r2w[ADDR_WIDTH-2:0]});

assign rempty = (raddr_gray_reg == addr_w2r);

dual_port_RAM #(.DEPTH(DEPTH),

.WIDTH(WIDTH)) dual_port_RAM_0 (.wclk(wclk),

.wenc(winc && ~wfull),

.waddr(waddr[ADDR_WIDTH-1:0]),

.wdata(wdata),

.rclk(rclk),

.renc(rinc && ~rempty),

.raddr(raddr[ADDR_WIDTH-1:0]),

.rdata(rdata));

endmodule

这里遇到一个问题,反复查看代码,怎么也找不出来,哭了!!!

最后一查,实例化RAM的时候,有个线连错了,最后通过,奥里给!!!

==========================================================================================

参考文献

声明

本人所有系列的文章,仅供学习,不可商用,如有侵权,请告知,立删!!!

本人主要是记录学习过程,以供自己回头复习,再就是提供给后人参考,不喜勿喷!!!

如果觉得对你有用的话,记得收藏+评论!!!

智能推荐

while循环&CPU占用率高问题深入分析与解决方案_main函数使用while(1)循环cpu占用99-程序员宅基地

文章浏览阅读3.8k次,点赞9次,收藏28次。直接上一个工作中碰到的问题,另外一个系统开启多线程调用我这边的接口,然后我这边会开启多线程批量查询第三方接口并且返回给调用方。使用的是两三年前别人遗留下来的方法,放到线上后发现确实是可以正常取到结果,但是一旦调用,CPU占用就直接100%(部署环境是win server服务器)。因此查看了下相关的老代码并使用JProfiler查看发现是在某个while循环的时候有问题。具体项目代码就不贴了,类似于下面这段代码。while(flag) {//your code;}这里的flag._main函数使用while(1)循环cpu占用99

【无标题】jetbrains idea shift f6不生效_idea shift +f6快捷键不生效-程序员宅基地

文章浏览阅读347次。idea shift f6 快捷键无效_idea shift +f6快捷键不生效

node.js学习笔记之Node中的核心模块_node模块中有很多核心模块,以下不属于核心模块,使用时需下载的是-程序员宅基地

文章浏览阅读135次。Ecmacript 中没有DOM 和 BOM核心模块Node为JavaScript提供了很多服务器级别,这些API绝大多数都被包装到了一个具名和核心模块中了,例如文件操作的 fs 核心模块 ,http服务构建的http 模块 path 路径操作模块 os 操作系统信息模块// 用来获取机器信息的var os = require('os')// 用来操作路径的var path = require('path')// 获取当前机器的 CPU 信息console.log(os.cpus._node模块中有很多核心模块,以下不属于核心模块,使用时需下载的是

数学建模【SPSS 下载-安装、方差分析与回归分析的SPSS实现(软件概述、方差分析、回归分析)】_化工数学模型数据回归软件-程序员宅基地

文章浏览阅读10w+次,点赞435次,收藏3.4k次。SPSS 22 下载安装过程7.6 方差分析与回归分析的SPSS实现7.6.1 SPSS软件概述1 SPSS版本与安装2 SPSS界面3 SPSS特点4 SPSS数据7.6.2 SPSS与方差分析1 单因素方差分析2 双因素方差分析7.6.3 SPSS与回归分析SPSS回归分析过程牙膏价格问题的回归分析_化工数学模型数据回归软件

利用hutool实现邮件发送功能_hutool发送邮件-程序员宅基地

文章浏览阅读7.5k次。如何利用hutool工具包实现邮件发送功能呢?1、首先引入hutool依赖<dependency> <groupId>cn.hutool</groupId> <artifactId>hutool-all</artifactId> <version>5.7.19</version></dependency>2、编写邮件发送工具类package com.pc.c..._hutool发送邮件

docker安装elasticsearch,elasticsearch-head,kibana,ik分词器_docker安装kibana连接elasticsearch并且elasticsearch有密码-程序员宅基地

文章浏览阅读867次,点赞2次,收藏2次。docker安装elasticsearch,elasticsearch-head,kibana,ik分词器安装方式基本有两种,一种是pull的方式,一种是Dockerfile的方式,由于pull的方式pull下来后还需配置许多东西且不便于复用,个人比较喜欢使用Dockerfile的方式所有docker支持的镜像基本都在https://hub.docker.com/docker的官网上能找到合..._docker安装kibana连接elasticsearch并且elasticsearch有密码

随便推点

Python 攻克移动开发失败!_beeware-程序员宅基地

文章浏览阅读1.3w次,点赞57次,收藏92次。整理 | 郑丽媛出品 | CSDN(ID:CSDNnews)近年来,随着机器学习的兴起,有一门编程语言逐渐变得火热——Python。得益于其针对机器学习提供了大量开源框架和第三方模块,内置..._beeware

Swift4.0_Timer 的基本使用_swift timer 暂停-程序员宅基地

文章浏览阅读7.9k次。//// ViewController.swift// Day_10_Timer//// Created by dongqiangfei on 2018/10/15.// Copyright 2018年 飞飞. All rights reserved.//import UIKitclass ViewController: UIViewController { ..._swift timer 暂停

元素三大等待-程序员宅基地

文章浏览阅读986次,点赞2次,收藏2次。1.硬性等待让当前线程暂停执行,应用场景:代码执行速度太快了,但是UI元素没有立马加载出来,造成两者不同步,这时候就可以让代码等待一下,再去执行找元素的动作线程休眠,强制等待 Thread.sleep(long mills)package com.example.demo;import org.junit.jupiter.api.Test;import org.openqa.selenium.By;import org.openqa.selenium.firefox.Firefox.._元素三大等待

Java软件工程师职位分析_java岗位分析-程序员宅基地

文章浏览阅读3k次,点赞4次,收藏14次。Java软件工程师职位分析_java岗位分析

Java:Unreachable code的解决方法_java unreachable code-程序员宅基地

文章浏览阅读2k次。Java:Unreachable code的解决方法_java unreachable code

标签data-*自定义属性值和根据data属性值查找对应标签_如何根据data-*属性获取对应的标签对象-程序员宅基地

文章浏览阅读1w次。1、html中设置标签data-*的值 标题 11111 222222、点击获取当前标签的data-url的值$('dd').on('click', function() { var urlVal = $(this).data('ur_如何根据data-*属性获取对应的标签对象