”DDR3“ 的搜索结果

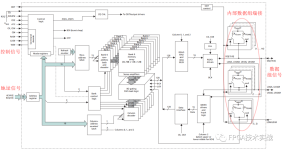

图1、7系列FPGA DDR3解决方案1.1 用户FPGA逻辑(User FPGA Logic)如图1中①所示,用户FPGA逻辑块是任何需要连接到外部DDR2或DDR3 SDRAM的FPGA设计。用户FPGA逻辑通过用户接口连接到内存控制器。1.2 用户接口(User ...

DDR3的读写和测试方法

DDR3 基础知识分享

标签: fpga开发

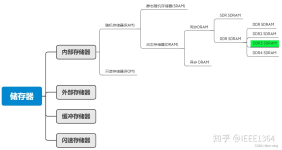

DDR3 SDRAM常 简称 DDR3 是当今较为常见的一种储存器,在计算机及嵌入式产品中得到广泛应用,特别是应用在涉及到大量数据交互的场合,比如电脑的内存条。对DDR3的读写操作大都借助IP核来完成,本次实验将采用 Xilinx...

通俗理解DDR3(自学使用)

标签: fpga开发

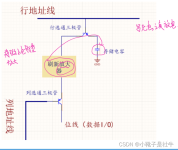

上述给出了DDR3的状态转移图,对于DDR3 SDRAM 来说,其工作是需要不断的进行刷新的,而且刷新时间是固定的(他是所有的bank一行一行进行刷新,bank同时刷新),假设行地址有12根地址线,那么就是有4096行,刷新假设...

DDR3读写测试程序,赛灵思平台验证测试

DDR4和DDR5相对于DDR3都提供了更高的性能和效率。然而,它们需要配备相应的主板和处理器才能正常运行,并且价格相对较高。选择哪种内存类型取决于您的具体需求和预算。如果您的计算机用途较为简单,DDR3内存已经足够...

内容名称:DDR3(APP/Naive 接口)工程代码 工程环境:Xilinx VIVADO 2018.3 内容概要:使用 Xilinx VIVADO 中的 MIG IP 核,读写位宽设置为 128 比特,并设计了外部读写模块 Verilog 代码,直接对 Xilinx 定义的 ...

此文档对于JESD标准DDR4和DDR3做中文解读,轻松理解DDR4/DDR3标准。 问题举例: ** 你真的理解SDRAM的S吗? ** 为什么Write一般是Center Aligned, Read是Edge Aligned? ** DDR4为什么没有Vref DQ? ** Mode Register可...

此文档对于JESD标准DDR5/DDR4/DDR3做中文解读,轻松理解DDR5/4/3标准。 问题举例: ** DDR5设计目标 ** 为什么Write一般是Center Aligned, Read是Edge Aligned? ** DDR5 Sub Channel设计的优势 ** DDR4 DIMM vs DDR5...

DDR2 DDR3 DDR4 FBGA内存ALTIUM PCB封装库, 3D封装库,型号列表如下: Component Count : 4 Component Name ----------------------------------------------- DDR2 WBGA84 DDR3_FBGA78 DDR3_FBGA96 DDR4_FBGA96

DDR3内存已经被广泛地使用,专业的PCB设计工程师会不可避免地会使用它来设计电路板。本文为您提出了一些关于DDR3信号正确扇出和走线的建议,这些建议同样也适用于高密度、紧凑型的电路板设计。 DDR3设计规则和信号...

DDR3-硬件设计和-Layout-设计官方设计参考资料.pdf

ddr3_ddr3l_power DDR3 DDR3L功耗计算工具 简单选择就可以直接算出来每个DDR颗粒的功耗大小,里面包含了DDR3的datesheet 系统配置介绍,功耗计算明细

本文档为DRAM技术精解 DDR3_DDR4_DDR5_LPDDR3_LPDDR4_LPDDR5 中文版第二版. 本文档详细介绍了Dram的历史发展中出现的不同技术,以及技术对应的解决方案 这是最详细的介绍, 把基本DDR 到DDR5,LPDDR 到LPDDR5的所有...

包括DDR2、DDR3、DDR4、DDR5规范,此外还有测试指导、layout指导,硬件设计指导。

1.镁光DDR3颗粒MT41K512M16HA-125AIT用户手册 2.Xilinx的Ug586MIG使用手册

DDR3控制器,基于Altera平台,修改管教后直接可以下载进PFGA

DDR2、DDR3、DDR4、DDR5规范,此外还有测试指导、layout指导,硬件设计指导

spartan6 里使用DDR3IP核,有教程以及源码

本文档为DRAM Technology DDR3_DDR4_DDR5_LPDDR3_LPDDR4_LPDDR5技术精解 中文版. 本文档详细介绍了dram的历史发展中出现的不同技术,以及技术对应的解决方案 这是最详细的介绍, 把基本DDR 到DDR5,LPDDR 到LPDDR5的...

基于K7的FPGA的DDR3读写程序,通过串口发送1024位的数据,写到FPGA的DDR3端,然后将数据从DDR3中读取出来,通过串口发送到PC端。

DSP6678DDR初始化和配置的代码。

DDR3 在布线中十分重要,它必须考虑阻抗匹配问题,通常单端为 50Ω,差分 100Ω。 图 3 给出了 DDR 及其去耦电容的最终布局,其中左图是顶层布局,右图为底层布局,共计 4 片 DDR3 芯片,顶层、底层各两片。 DDR ...

DDR3 SDRAM内存的总线速率达到600 Mbps to 1.6 Gbps (300 to 800 MHz),1.5V的低功耗工作电压,采用90nm制程达到2Gbits的高密度。这个架构毫无疑问更快、更大,每比特的功耗也更低,但是如何实现FPGA和DDR3 SDRAM ...

FPGA实现DDR3控制器

DDR3开发必备,内容由标准的英文版本翻译而来,对开发DDR3 DRAM的开发者由很大的帮助。DDR3属于SDRAM家族的存储器产bai品,提供相较于DDR2 SDRAM更高的运行性能与更低的du电压,是DDR2 SDRAM(四倍数据率同步动态...

技嘉B150M D3H DDR3魔改BIOS,支持市面上大多数魔改QNCT,E3V5,6789代CPU.不能超过6核12线程,否则会拉胯供电。89代要屏蔽,否则烧毁针脚。

推荐文章

- 【解决报错】java.sql.SQLException: Access denied for user 'root'@'localhost' (using password: YES)-程序员宅基地

- echart y轴显示小数或整数_echarts y轴显示16位小数-程序员宅基地

- Android客户端和Internet的交互_android与internet-程序员宅基地

- linux新建分区步骤_linux创建基本分区的步骤-程序员宅基地

- 信号处理-小波变换4-DWT离散小波变换概念及离散小波变换实现滤波_dwt离散小波变换进行滤波-程序员宅基地

- Ubuntu 10.10中成功安装ns-allinone-2.34_进入/home/ubuntu1/ns-allinone-2.34目录cd /home/ubuntu1-程序员宅基地

- 使用AES算法对字符串进行加解密_java 判断aes加密 与否-程序员宅基地

- DFS深度优先搜索(前序、中序、后序遍历)非递归标准模板_深度优先搜索 无递归-程序员宅基地

- 程序员面试字节跳动,被怼了~_字节跳动java什么技术站-程序员宅基地

- 嵌入式软考备考(五)安全性基础知识-程序员宅基地