”DDR3详解“ 的搜索结果

个人觉得比较经典的DDR3 SDRAM工作原理详解,对初学者和一般开发者用处较大 相关下载链接://download.csdn.net/download/weixin_42968039/10603409?utm_source=bbsseo

DDR内存是什么意思 DDR3和DDR4内存区别分析【详解】 - 知乎 DDR内存是什么? 内存是电脑中重要的核心部件之一,内存是其它硬件与CPU进行沟通的桥梁。计算机中所有程序的运行都是在内存中进行的。 专业来说...

DDR3的一些基本知识

标签: 开发语言

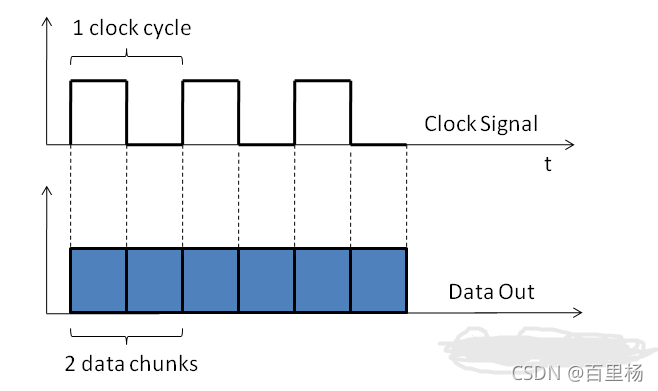

记录一下DDR3文档查阅后的总结:DDR的带宽决定数据能承载的容量;

深入了解㟓内存,DRAM技术详解

ddr3开头的都是要接到ddr3上的只需要按照电路设置IO口即可,我们只需要控制左侧接口。1、打开官方文件,官方已经给出接口和例化方式。每个接口的详细介绍可以去看官方文档。下面是我对每个接口的简单理解。

这部分的讲述运用DDR3的简化时序图。 DDR3的内部是一个存储阵列,将数据“填”进去,你可以它想象成一张表格。和表格的检索原理一样,先指定一个行(Row),再指定一个列(Column),我们就可以准确地找到所...

结合串口接收模块和 tft 显示屏控制模块,设计一个基于 DDR3—Native接口的串口传图帧缓存系统。

ISE 中基于mig IP完成DDR3的循环测试项目简述MIG接口的简单描述MIG IP的读写时序MIG IP的读写测试代码 项目简述 该项目的描述是,FPGA向DDR3芯片写入数据,然后再读出数据,从而验证读写模块的正确性。该项目具有...

DDR系列内存详解及硬件设计规范-希望对您有帮助

WSTRB[n:0] 信号为高电平时,指定包含有效信息的数据总线的字节通道。

内存系列一:快速读懂内存条标签 内存是我们平常接触最频繁的计算机硬件之一,内存的大小、...小张有一定的计算机背景知识,最近他在京东上买了两条DDR3的内存,打算把笔记本升级成8G。可是一拆开包装到就傻眼了: ...

DDR4技术原理是基于前代DDR3的改良和升级。它主要有以下几个方面的原理: 首先,DDR4采用了更高的频率,一般可以达到2133MHz以上,高频率可以提高数据传输速度,提高内存的读写效率。 其次,DDR4采用了更高的数据...

关于DDR协议的一些操作的理解3

标签: 开发语言

3.DDR中的write leaving。2.DDR中的差分信号。

结合串口接收模块和 tft 显示屏控制模块,设计一个基于 DDR3 的Native接口串口传图帧缓存系统。

一、假设由vivado创建的DDR IP核名称为“ddr3”,则存在如下的目录结构:├─ddr3│ ├─docs│ ├─example_design│ │ ├─par│ │ ├─rtl│ │ │ └─traffic_gen│ │ ├─sim│ │ └─synth...

详解DDR3的四种ODT功能模式

DDR3内存详解,存储器结构+时序+初始化过程 标签:DDR3存储器博客 2017-06-17 16:101943人阅读评论(1)收藏举报 分类: 硬件开发基础(2) 转自:...

对于点对多点的连接,如DIMM条或分立...建议DDR信号布线顺序:电源(包括VTT岛链及端接电阻,VREF),数据,地址/命令,控制,时钟,反馈。7、 如果布局允许,将 VTT发生器放置在VTT岛链的中间或尽可能靠近岛链的末端;

Xlinx的MIG IP核是官方给出的DDR驱动,是一个FPGA工程师由入门更近一步必学的一个IP,因为FPGA本身的优势就是吞吐量特别大,而这一定伴随着内存的操作。Xlinx的软件版本主要有ISE与vivado两个软件,两个软件MIG的...

推荐文章

- Windows系统鼠标右键菜单添加打开cmd终端_we右键进入cmd-程序员宅基地

- python汇编语言还是机器语言_深入理解计算机系统(3.1)------汇编语言和机器语言...-程序员宅基地

- android毕设各种app项目,安卓毕设,android毕设_app毕业设计-程序员宅基地

- Keil侧边工具栏(项目窗口)打开方式_keil侧边栏-程序员宅基地

- 算法学习,转载记录(持续记录)-程序员宅基地

- 局域网探测器_局域网检测-程序员宅基地

- 【C语言基础系列,阿里java面试流程_c语言java面试-程序员宅基地

- Linux技术简历项目经验示例(二)_linux简历工作经验怎么写-程序员宅基地

- 安卓手机软键盘弹出后不响应onKeyDown、onBackPressed方法解决方案-程序员宅基地

- 使用二维数组实现存储学生成绩_c#创建控制台应用程序studentscore,生成学生成绩单——二维数组的使用。-程序员宅基地