”FPGA二分频代码“ 的搜索结果

FPGA经验谈

参考:正点原子开拓者 FPGA 开发指南 数字频率计是一种基本的测量仪器,被广泛应用于航天、电子、测控等领域。基于传统测频原理的频率计的测量精度将随被测信号频率的下降而降低,在使用中有较大的局限性,而等精度...

代码如下。 module fp_even(clk_in,rst_n,clk_out); input clk_in; input rst_n; output clk_out; reg [1:0] cnt; reg clk_out; parameter N=6; always @ (posedge clk_in or negedg...

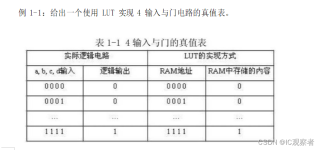

FPGA基础(数字电路)

标签: fpga开发

Verilog语言是硬件描述语言而不是设计语言。在写Verilog代码时,大脑要先想好完成的具体功能应该用什么样的电路实现,然后再用Verilog描述出来。

关于EEPROM学习的小结。其中相关代码来自正点原子、相关资料来自米联客。

# 章节一:FPGA中的时钟管理概述 ## 1.1 FPGA中时钟的重要性 时钟在FPGA中扮演着至关重要的角色,它不仅仅是用来同步各个部分的操作,更是系统性能和稳定性的关键因素。FPGA中的时钟资源通常是有限的,合理而有效...

DDR3 SDRAM(Double Data Rate 3 Synchronous Dynamic RAM),即第三代双倍速率同步动态随机存储器。本系列文章尝试剖析缓存技术的基础原理,并通过FPGA进行实现。

3设计内容 3.1基本状态设计 1、采用信号并置处理很多输入信号的方式: always @(call_up_1 or call_up_2 or call_up_3 or call_up_4 or call_up_5) up_all={1’b0, call_up_5, call_up_4, call_up_3, call_up_2, ...

基于FPGA的出租车计费器的设计

标签: fpga

这个代码是整个库文件包工程的一部分,希望能在两年的时间写出完整的包,但是时间也不多,只能晚上空闲时断断续续写的,毕竟不能耽误打游戏不是- 该工程的地址分享在gitee,建议直接看gitee的,vlog的代码不会更新。...

even_div

基于FPGA的按键消抖

标签: fpga开发

那么对于计时器时间的选择,一般抖动时间取决于机械结构,一般就10ms左右,如果不同你也可以通过查询使用的按键或者自己写一个慢慢该数据看现象来确定,然后按下时间一般就取决于操作员,但是正常按键的话一般都是在...

串口通信之串口发送数据,每10ms发送一个数据,每次发送的数据比前一个数据大一;发送一四十位数据。

**概念:**对FPGA频率较高的系统时钟进行分频可以产生频率较低的分频时钟。 应用:分频时钟可以作为FPGA低速外设的同步时钟,比如 IIC总线时钟(<= 400KHz) 低速SPI总线时钟(<=1MHz) **注:**对于频率较高...

1.不同开发板的引脚不同,需根据自己开发板重新配置引脚2.不同开发板的数码管高低电平有效不同,使用前需参考原理图3.数码管刷新频率采用1KHZ原因:频率过快(50MHZ)和频率过慢(1HZ)都会导致数码管显示不稳定,故...

逻辑设计也是这样:如果不按规范做的话,过一个月后调试时发现有错,回头再看自己写的代码,估计很多信号功能都忘了,更不要说检错了;如果一个项目做了一半一个人走了,接班的估计得从头开始设计;如果需要在原来的...

相关文章: Verilog设计(二):分频电路设计 ... 基于verilog的分频器设计(奇偶分频原理及其电路实现:上) https://www.cnblogs.com/Fun-with-FPGA/p/4700631.html D触发器实现二分频电路(D触发器构成的2分...

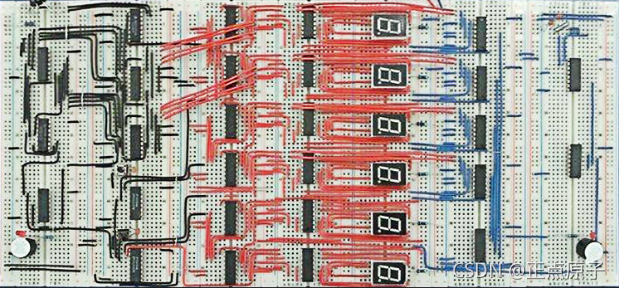

使用FPGA开发板上的6位数码管以动态方式从0开始计数,每100ms计数值增加1,当计数值从0增加到999999后重新从0开始计数。 二、背景简介 1、 动态数码管的是意思是,依次轮流让六个数码管显示数字,只要这个轮流的时间...

推荐文章

- php 上传图片 缩略图,PHP 图片上传类 缩略图-程序员宅基地

- scrapy爬虫框架_3.6.1 scrapy 的版本-程序员宅基地

- 微信支付——统一下单——java_小程序统一下单接口-程序员宅基地

- (已解决)报错 ValueError: Tensor conversion requested dtype float32 for Tensor with dtype resource-程序员宅基地

- 记录el-table树形数据,默认展开折叠按钮失效_eltable一刷新展开的子节点展开按钮消失-程序员宅基地

- 设计模式复习-桥接模式_csdn天使也掉毛-程序员宅基地

- CodeForces - 894A-QAQ(思维)_"qaq\" is a word to denote an expression of crying-程序员宅基地

- java毕业生设计移动学习网站计算机源码+系统+mysql+调试部署+lw-程序员宅基地

- 14种神笔记方法,只需选择1招,让你的学习和工作效率提高100倍!_1秒笔记 高级-程序员宅基地

- 最新java毕业论文英文参考文献_计算机毕业论文javaweb英文文献-程序员宅基地