优异的cache性能很大程度上依赖于cache lines(缓存行)的重复使用,优化的最主要目标也在于此,一般通过恰当的数据和代码内存布置,以及调整CPU的内存访问顺序来达到此目的。由此,应该熟悉cache内存架构,特别是...

”cache,优化“ 的搜索结果

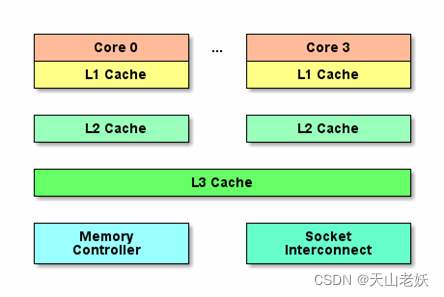

一、cache特点六讲 存储器是分层次的,离CPU越近的存储器,速度越快,每字节的成本越高,同时容量也因此越小。寄存器速度最快,离CPU最近,成本最高,所以个数容量有限,其次是高速缓存(缓存也是分级,有L1,L2等...

由于技术的发展,片上多核处理器上的核数量和片上缓存的大小一直在增长,且缓存占据了芯片的大部分面积,使得片上缓存所消耗的能量成为存储器子系统中功率损耗的主要贡献者,因此对片上缓存进行优化是提高存储器系统...

作为通用优化设置,建议将vm.dirty_background_ratio设置为5%,vm.dirty_ratio设置为10%。(参考值,设置为这两个值效果还是不错的)当写入只是将数据暂时存入pagecache,并且置为dirty标志,写入pagecache的数据会...

Java虚拟机中的动态锁cache优化

为了提供高速的数据访问,多核处理器常使用Cache划分机制来分配二级Cache资源,但传统的共享Cache划分算法大多是面向多道程序的,忽略了多线程负载中共享和私有数据访问模式的差别,使得共享数据的使用效率降低....

基于TMS320DM642的视频编码Cache优化策略、电子技术,开发板制作交流

本文以 TI C6000 系列芯片为例 ,从分析它的 Cache 结构出发 ,利用直接存 储器存取 DMA (Direct Memory Access) 设计了一种双缓冲区结构 ,以减少片内、外存储器之间数据交换的时间 ,并针对高斯滤波函数加以实 现。...

片上多处理器末级Cache优化技术研究.pdf

面向多核处理器的共享cache优化研究进展.pdf

VPP高性能从何而来之一:cache优化cache优化包括如下几个方面1.cache line 对齐2.尽量避免cache一致性问题3.I-cache与D-cache cache优化包括如下几个方面 1.cache line 对齐 2.尽量避免cache一致性问题 3.I-...

好文要转,太棒了~~~~~~~~~~~~~~~~~~~~~~~~~ ...昨晚为了优化这个题目弄到2点多,今天一早就写博,我真是太不蛋定了,哈哈。 做OJ的朋友都知道快速幂,我就不罗嗦了,我说的主要是矩阵乘法实现层面的优化。

背景 监控线上实例时,曾出现可用内存不足,性能发生抖动的情况。研究后发现是日志文件的page cache占用了大量的内存(200G+),导致系统可立即分配的内存不足,影响了系统性能...据此,考虑能否设计一个优化,在page

之前写了一篇关于c/c++优化的一点建议,被各种拍砖和吐槽,有赞成的有反对的,还有中立的,网友对那篇博客的的评论和吐槽,我一个都没有删掉,包括一些具有攻击性的言论。笔者有幸阅读过IBM某个项目的框架代码,和我...

度量标准 Reducing the hit time(降低命中时间):更小的更简单...Increasing cache bandwidth(提高Cache带宽):Pipelined caches, multibanked caches, and nonblocking caches。这些技术对能耗有着不同的影响。 R

cache性能优化总结

标签: cache优化

cache性能优化总结

Degrees of Latency ...The latency of data access becomes greater with each cache level. Latency of memory access is best measured in CPU clock cycles. One cycle occupies from 4 to 6 nanoseconds, dep

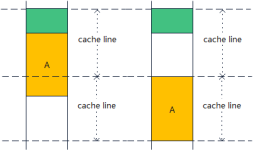

优异的cache性能很大程度上依赖于cache lines的重复使用,优化的最主要目标也在于此,一般通过恰当的数据和代码内存布置,以及调整CPU的内存访问顺序来达到此目的。由此,应该熟悉cache内存架构,特别是cache内存...

cache 优化基础

标签: cache,优化

简单介绍了dsp中的cache原理,为做Cache优化提供理论基础。

dsp cache优化(转载) 2010年07月27日 星期二 12:22 转载自 8kone8 最终编辑 zcug_071 以前我自己编写过乒乓结构的程序,后来查资料的时候发现乒乓结构还是很普遍的用法,但是我是初学者,其实编程优化...

本文主要介绍TI C6000系列的C64x+的DSP Cache配置,常见的Cache miss模式以及如何在多核或者多外设DMA系统下维护Cache一致性,当然还有Cache优化的专题,针对指令L1P和数据L1D cache的优化。 C64x+与C64x CACHE的...

DPDK利用了一系列的Cache软件优化方法(cache预取,cache对齐,hugepage ,NUMA感知,DDIO)高效的减少访存开销以提升性能。本文将讲解这些方法的基本原理以及在DPDK中的应用。1:Cache预取Cache由于时间以及空间上...

转载来源:http://blog.chinaunix.net/uid-7319742-id-2059720.html

Cache 优化

标签: cache 优化 processing

对于一般的CPU信号处理加上外围设备的DMA数据读写情况,处理方法是在内存中开辟pingpong缓冲区。inbufa,outbufa,inbufb,outbufb四块内存区,当CPU处理inbufa的数据并将产生的结果放到outbufa,这是外围器件DMA搬移...

推荐文章

- Android RIL框架分析-程序员宅基地

- Python编程基础:第六节 math包的基础使用Math Functions_ps math function-程序员宅基地

- canal异常 Could not find first log file name in binary log index file_canal could not find first log file name in binary-程序员宅基地

- 【练习】生成10个1到20之间的不重复的随机数并降序输出-程序员宅基地

- linux系统扩展名大全,Linux系统文件扩展名学习-程序员宅基地

- WPF TabControl 滚动选项卡_wpf 使用tabcontrol如何给切换的页面增加滚动条-程序员宅基地

- Apache Jmeter常用插件下载及安装及软硬件性能指标_jmeter插件下载-程序员宅基地

- SpringBoot 2.X整合Mybatis_springboot2.1.5整合mybatis不需要配置mapper-locations-程序员宅基地

- ios刷android8.0,颤抖吧 iOS, Android 8.0正式发布!-程序员宅基地

- 【halcon】C# halcon 内存暴增_halcon 读二维码占内存-程序员宅基地