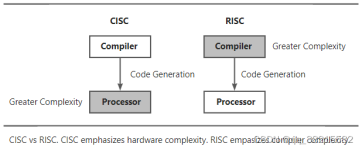

RISC全称Reduced Instruction Set Compute,精简指令集计算机。 CISC全称Complex Instruction Set Computers,复杂指令集计算机。 CISC既有简单指令也有复杂指令,后来人们发现典型程序中80%的语句都是使用计算机...

”risc“ 的搜索结果

官方最新的riscv-debug-spec,几乎兼容之前的debug0.13.x,修复bug和不兼容请看1.2.1

RARS-RISC-V汇编程序和运行时模拟器RISC-V汇编器,模拟器和运行时RARS将汇编和模拟RISC-V汇编语言程序的执行。 它的主要目标是为开始使用RISC-V的人们提供一个有效的开发环境。特征RISC-V IMFDN基础(riscv32和riscv...

软设之CISC和RISC

标签: 笔记

指令特点是数量少,使用频率接近,定长格式,大部分是单周期指令,操作寄存器,只有Load/Store操作内存。实现方式:增加了通用寄存器,硬布线逻辑...RISC是精简指令系统。寻址方式是多选址方式。寻址方式:支持方式少。

以计算两张图像的 alpha 混合为例...隼瞻科技自研的代码密度增强技术,结合处理器指令集、编译器和基础库,面向应用深度优化的这一超级组合拳,为行业客户带来实实在在的平替助力,同时也为RISC-V生态发展提供源动力。

RISC架构是指在计算机体系结构中,指令集包含较少且简单的指令,这些指令执行的操作也较为简单。与之相对,CISC架构指令集则更为复杂,包含更多、更复杂的指令。RISC架构致力于简化指令集,通过分解复杂指令为多个...

RISC-V中文手册.pdf

标签: risc-v

RISC-V中文手册.pdf

前面我们使用 verilog 完成了一个 risc-v cpu 的设计,但 cpu 最终也是为了程序服务的,不能执行程序的 cpu 没有任何意义。所以这一节我们要研究如何在自己设计的 cpu 上运行 C 程序。

riscv-tools构建脚本中的默认设置将构建可以针对任何 RISC-V ISA 的编译器、汇编器和链接器,但这些库是为 RV32G 和 RV64G 目标构建的。按照以下说明构建针对纯 RV32I CPU 的完整工具链(包括库)。 以下命令将为纯...

RISC-V-On-PYNQ Overlay实现了在PYNQ-Z2板上的RISC-V处理器及工具链集成,并提供了完整的RISC-V源码与设计流程,得益于PYNQ软件框架,其支持在Jupyter Notebook对RISC-V进行编译、调试与验证,即可以在Jupyter ...

探索未来计算:RISC-V架构下的QEMU模拟器 项目地址:https://gitcode.com/riscv/riscv-qemu RISC-V QEMU是一个令人兴奋的开源项目,它提供了在RISC-V指令集架构上运行多种操作系统和应用程序的能力。该项目的目标是为...

RISC-V Card:探索开源处理器架构的新篇章 项目地址:https://gitcode.com/jameslzhu/riscv-card RISC-V Card 是一个创新的、基于RISC-V指令集架构(ISA)的教育和实验平台。该项目旨在帮助开发者、学生和硬件爱好者...

本人小白一枚,在学习FPGA的过程中偶然刷到了tinyriscv这个开源项目,并且自己对计算机体系结构的知识也很感兴趣,所以想参考这个开源项目做一个基于RISC-V指令集的CPU

基于 Logisim 的 RISC-V 处理器设计(单周期)

RISC-V入门指南 这是的存储库,该是RISC-V基金会准备的入门资料,托管在Read The Docs中,以向您显示从哪里开始,如果您有兴趣开发免费和开源的ISA。 有关RISC-V本身的详细信息,请参见。 您也可以为《入门指南》...

探索未来计算新星:RISC-V 指令集架构指南 项目地址:https://gitcode.com/mikeroyal/RISC-V-Guide 在计算机科学的世界中,指令集架构(ISA)是硬件与软件之间的桥梁,它定义了处理器如何执行程序。近年来,一个名为...

探索KianRiscV:一款高效的开源RISC-V架构处理器 项目地址:https://gitcode.com/splinedrive/kianRiscV 项目简介 KianRiscV是一个开放源代码的RISC-V架构处理器设计项目,由Splinedrive开发并维护。该项目的目标是...

摆烂才是王道

RISC-V-单周期核心-Logisim。介绍: 该存储库包含在Logisim上模拟的RISC-V单周期32位处理器。 该电路包含两个RAM MAR(存储器地址寄存器)的32位ALU,32位数据总线,16KB ROM / RAM,12位地址总线。 寄存器文件包含...

探索RISC-V架构的新里程:riscv-opcodes项目详解 项目地址:https://gitcode.com/riscv/riscv-opcodes 在计算机科学的世界中,处理器指令集架构(ISA)是硬件与软件之间的桥梁。RISC-V作为近年来备受瞩目的开放源代码...

选择CISC还是RISC架构取决于应用需求、软件生态、性能和能效目标等多种因素。RISC架构由于其高效和能效的特点,在嵌入式系统、移动设备和最近的服务器市场中特别受欢迎。而CISC架构,特别是x86架构,由于其强大的...

32位RISC微处理芯片设计和8位RISC微控制芯片研制获得成功代表国内微处理器最高水平的专用嵌埋式32位RISC芯片设计工作已由清华大学微电子学研究所完成,其逻辑和电路模拟、指令验证等都取得满意结果...

讲述RISC-V的体系结构及指令

WCH RISC CH32V303RCT6单片机的SDI Printf虚拟串口功能类似RTT打印功能简单分析,无需硬件串口也可以打印调试信息了

探索RISC-V架构:riscv-isa-sim - 轻松模拟与验证 项目地址:https://gitcode.com/riscv/riscv-isa-sim riscv-isa-sim 是一个开放源码的RISC-V指令集模拟器,由RISC-V基金会维护,旨在帮助开发者和研究人员在不同环境...

RISC-V 汇编器和运行时模拟器。 它是用 Java 编写的,能够模拟基本整数 ISA( I扩展)加上M和F扩展( RV32IMF )的所有指令,包括用户级指令集手册1 中描述的所有伪指令。 它的开发考虑到它可以用于各种课程,例如:...

bex 是用 SystemVerilog 编写的生产级开源 32 位 RISC-V CPU 内核。CPU 内核高度可参数化,非常适合嵌入式控制应用。Ibex 正在接受广泛的验证,并且已经看到多个流片。Ibex 支持整数 (I) 或嵌入式 (E)、整数乘除法 ...

电子科技大学CPU设计:精简指令集(RISC)32位单周期cpu设计.pdf电子科技大学CPU设计:精简指令集(RISC)32位单周期cpu设计.pdf电子科技大学CPU设计:精简指令集(RISC)32位单周期cpu设计.pdf电子科技大学CPU设计:精简...

推荐文章

- 回调函数使用详解_回调函数的用法-程序员宅基地

- [STM32F0xx]的AD转换驱动程序_stm32f0xx adc_in-程序员宅基地

- 优秀的程序员都热爱写作_程序员写作-程序员宅基地

- 为什么加深神经网络如此有效?从卷积滤波器解释_卷积深度变深什么作用-程序员宅基地

- Android Studio 混淆_android studio 开启混淆-程序员宅基地

- 专业学位计算机技术排名,山东师范大学计算机技术(专业学位)专业考研难度分析-专业排名-难度大小...-程序员宅基地

- idea配置tomcat环境_idea的tomcat,连接不显示explore-程序员宅基地

- 说说内核与计算机硬件结构-程序员宅基地

- 数据结构应用案例——栈结构用于8皇后问题的回溯求解-程序员宅基地

- c语言scanf中的分隔符的作用,C语言中scanf与分隔符(空格回车Tab)-程序员宅基地