”risc-v“ 的搜索结果

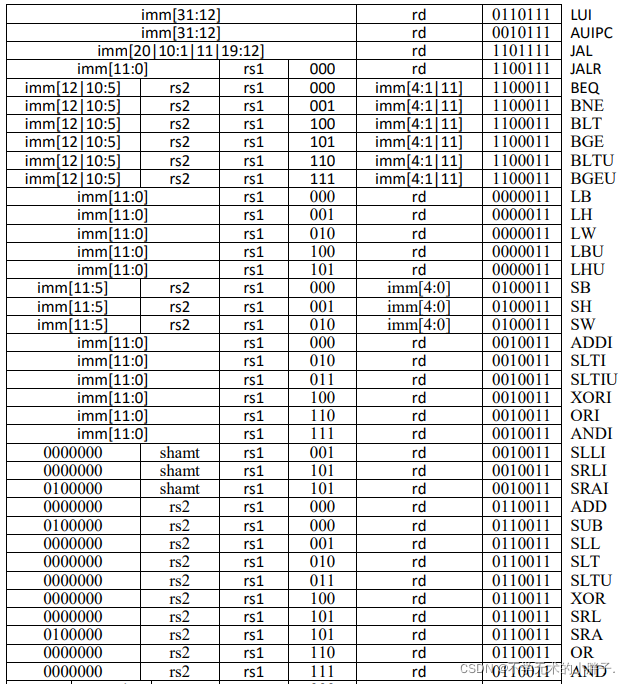

RISC-V架构采用了基于定长指令(Fixed-length instruction)和模块化设计方案。具体来说,RISC-V的指令长度为32位,在指令长度相同的前提下,RISC-V的指令数量比ARM、x86等指令集更少,使得其指令执行效率更高。此外...

第 一部分 CPU与RISC-V综述 第 1章 一文读懂CPU之三生三世 2 1.1 眼看他起高楼,眼看他宴宾客,眼看他楼塌了——CPU众生相 3 1.3 人生已是如此艰难,你又何必拆穿——CPU从业者的无奈 17 1.4 无敌是多么寂寞——...

RISC-V架构学习

标签: RISC-V

RISC-V架构RISC-V简介RISC-V起源RISC-V大事件RISC-V 指令特点设计哲学-简单就是美无病一身轻——架构的篇幅能屈能伸——模块化的指令集浓缩的都是精华——指令的数量RISC-V指令集简介模块化的指令子集规整的指令编码...

RISC-V特权级别

标签: risc-v

所以内核分两部分,运行在M模式下的代码为内核提供访问硬件资源的能力,而S模式下的代码则更加灵活。里的最高权限模式,它具有访问所有资源的权限,它的代码是百分百可信的,通常运行在这个模式下的为。...

物联网产业链专题报告-RISC-V大有可为.docx

本文采用RISC-V架构设计CPU,实现单周期CPU,设计取指、译码、执行、访存、写回五个阶段,扩展实现了RV32I指令集,通过该指令集所有指令的仿真测试。工具采用了iverilog和GTKwave。(具体仿真调试过程见下一篇文章)

随着摩尔定理的几近失效,传统的追求通用...介绍了开源芯片的作用和发展历史,讨论了有望成为下一代芯片开发根基的RISC-V指令集架构的特点和影响以及前端设计中的敏捷开发实践,并对芯片开发的新发展与不足做出了总结。

RISC-V指令集体系结构分析。

本人小白一枚,在学习FPGA的过程中偶然刷到了tinyriscv这个开源项目,并且自己对计算机体系结构的知识也很感兴趣,所以想参考这个开源项目做一个基于RISC-V指令集的CPU

总之,学习RISC-V需要掌握计算机系统的基础知识,熟悉RISC-V指令集架构和微体系结构,理解RISC-V的编程模型和编译工具链,并实践项目开发,才能真正掌握RISC-V的开发和应用。

引入: 简单的介绍一下X86、ARM、RISC-V三种cpu架构的区别和应用场景。X86、ARM和RISC-V是三种不同的CPU架构,它们在设计理念、指令集和应用场景上有一些区别。

RISC-V还是一个非常年轻的指令集架构,同时其十分瞩目精简、开源的特性也十分有利于我们学习,所以在未来的一段时间内,将把主要精力放在对RISC-V的指令集架构,包括基本指令集和拓展指令集的学习,不定时在此更新

RISC-V-Instruction_Level_Simulator

OpenV: 支持RV32的开源微处理器,Verilog,MIT Licensed,OnChipUIS,来源于哥伦比亚的Universidad Industrial de Santander。PicoRV32: Clifford Wolf设计的(针对FPGA)RV32微处理器,Verilog,ISC Licensed。...

基于 vscode+qemu 的risc-v学习环境的搭建

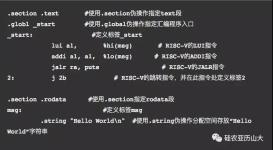

一文学懂risc-v汇编操作

标签: risc-v

深入浅出的介绍各种risc-v指令以及介绍程序是如何在内存中组织起来的。

本科毕业设计

推荐文章

- 用好ASP.NET 2.0的URL映射-程序员宅基地

- C语言等级考试是把题目删了,历年全国计算机的等级考试二级C语言上机考试地训练题目库及答案详解(72页)-原创力文档...-程序员宅基地

- Microsoft Office显示正在更新无法打开的问题_正在更新microsoft 365和office-程序员宅基地

- 非常好的Ansible入门教程(超简单)-程序员宅基地

- 【Gradle-8】Gradle插件开发指南-程序员宅基地

- 使用PL/SQL Developer软件解锁_plsqldev表格锁怎么打开-程序员宅基地

- 【Windows Server 2019】Web服务 IIS 配置与管理——配置 IIS 进阶版 Ⅳ_iis默认路径-程序员宅基地

- 网络中的各层协议_发送消息时各层协议-程序员宅基地

- UCRT: VC 2015 Universal CRT, by Microsoft_vc15rt-程序员宅基地

- 关于EntityFramework 7 开发学习_entiry framework 7 书籍-程序员宅基地