”同步复位“ 的搜索结果

大家好,我是数字小熊饼干,一个练习时长两年半的ic打工人。我在两年前通过自学跨行社招加入了IC行业。...复位信号可以分为同步复位和异步复位两种,它们各自有自己的优点和缺点,我们接下来对这两种复位信号进行介绍。

对常见三种复位方式(同步复位、异步复位、异步复位同步释放)进行介绍与分析,详细介绍了各种复位方式的优缺点,并进一步分析了异步复位同步释放的工作机理与优势所在。

异步复位同步释放电路

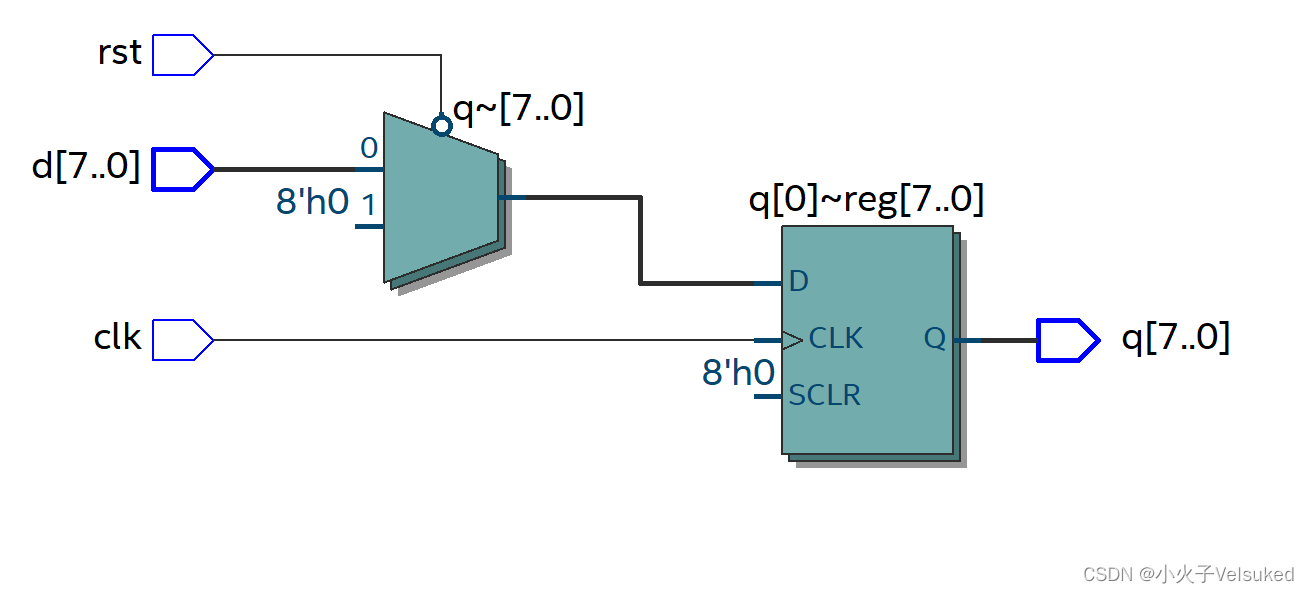

同步复位:顾名思义,同步复位就是指复位信号只有在时钟上升沿到来时,才能有效。否则,无法完成对系统的复位工作。用Verilog描述如下: always @ (posedge clk) begin if (!Rst_n) ... end 异步复

同步复位与异步复位的优缺点 同步复位的优点: 一般能够确保电路是百分之百同步的。 确保复位只发生在有效时钟沿,可以作为过滤掉毛刺的手段。 同步复位的缺点: 复位信号的有效时长必须大于时钟周期,...

verilog中同步复位,异步复位,同步释放优缺点以及PLL配置复位设计

复位电路是每个数字逻辑电路的重要组成部分之一。复位方式大致分为二类: 同步复位和异步复位

Verilog FPGA 同步 异步 复位

一般都推荐使用异步复位,同步释放的方式,而且复位信号低电平有效。这样就可以两全其美了。

一、同步复位与异步复位特点: 同步复位就是指复位信号只有在时钟上升沿到来时,才能有效。否则,无法完成对系统的复位工作。 异步复位是指无论时钟沿是否到来,只要复位信号有效,就对系统进行复位。 二、异步...

因此,此时第二级触发器的输出一定是稳定的低电平,方框左中触发器仍然处于复位状态。在下一个clk到来时,第一级触发器的输出已经是稳定的高电平了,故。我们在Gvim中更改了代码,VCS编译后,Verdi中还是旧的代码,...

到底是采用同步复位还是异步复位,全局复位还是局部复位,是由多方面的因素决定的。但良好的复位设计既可以提高系统的可靠性,又可以节省大量的逻辑资源。在实际应用中,笔者也看到过很多因为复位电路设计问题而导致...

注意:1.1)可以看出使用同步复位时,需要保证在复位时,需要有时钟的存在而且需要大于时钟周期,否则复位信号无法被捕获到该逻辑中。2)对复位信号的脉冲宽度有要求,必须大于指定的时钟周期,且很难保证复位信号...

同步复位和异步复位的优缺点

标签: fpga开发

从资源方面考虑:fpga底层寄存器如果是异步复位那么就使用异步复位的电路更节省资源,如果FPGA底层的寄存器是同步复位的,那么就使用同步复位的电路更节省资源。复位信号独立于时钟,只要复位信号发起,电路立即复位...

同步复位:是复位信号和时钟同步,当时钟上升沿检测到复位信号,执行复位操作。异步复位:它是指无论时钟沿是否到来,只要复位信号有效,就对系统进行复位。

【Verilog】 同步复位和异步复位比较 同步复位 sync 异步复位 async 特点 复位信号只有在时钟上升沿到来时才能有效。 无论时钟沿是否到来,只要复位信号有效,就进行复位。 Verilog描述 ...

IC芯片FPGA设计 异步复位同步复位电路设计verilog源码+Testbench仿真源码 module areset_srelease_tb(); reg rst_n; //?????? reg clk; //?? reg din; //???? wire dout; //???? areset_srelease u_areset_...

一、同步复位 定义:从名字来看,同步也就是和时钟同步的关系,一起发生变化。所以同步复位就是只有时钟上升沿到来时,才能产生有效变化;否则,无法产生对系统的复位操作。举个例子如下: //一个高电平有效的...

同步复位与异步复位-异步复位和同步复位区别-异步复位同步释放.doc

推荐文章

- 小说网站系统源码|PHP付费小说网站源码带app-程序员宅基地

- Swift编码规范_swift 正则判断文件类型-程序员宅基地

- 关于shell 中return用法解释(转)_shell return-程序员宅基地

- Linux编译宏BUILD_BUG_ON_ZERO-程序员宅基地

- c51语言单片机打铃系统设计,基于单片机的自动打铃系统的设计-程序员宅基地

- 在php中使用SMTP通过密抄批量发送邮件-程序员宅基地

- python数据清洗+数据可视化_python课程题目数据清除与可视化-程序员宅基地

- 【11g】3.3 Oracle自动存储管理存储配置_oraclestorageoptions-程序员宅基地

- signature=b2f9171fa2897cefe08a669efaf58433,FULFILLMENT TRACKING IN ASSET-DRIVEN WORKFLOW MODELING-程序员宅基地

- 宜兴市计算机中等学校,重磅!江苏省陶都中等专业学校正式揭牌!-程序员宅基地