verilog数字时钟设计功能说明问题分析及模块实现模24计数器模60计数器模6计数器模10计数器模60计数器数码管驱动电路11位控制位说明分频器数字时钟顶层文件实现写在后面 功能说明 本文实现一个采用同步计数,具有暂停...

”数字设计“ 的搜索结果

什么是数字IC后端设计? 完整的后端设计由后端半定制和后端全定制两个设计部分组成: 后端全定制设计是指在设计初期最先按照设计需求设计出的物理库单元,物理单元库由标准单元库、IP库及满足特殊需求的定制部件单元...

数字IC设计的前端设计和后端设计流程数字IC前端设计 数字IC前端设计 数字IC就是传递、加工、处理数字信号的集成电路(Integrated Circuit, IC), 近年来集成电路技术的飞速发展和广泛应用、IC品种也多种多样,按照IC...

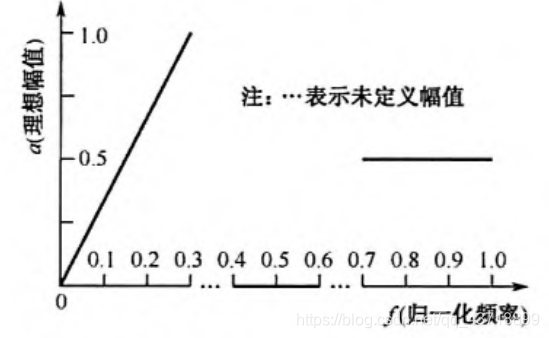

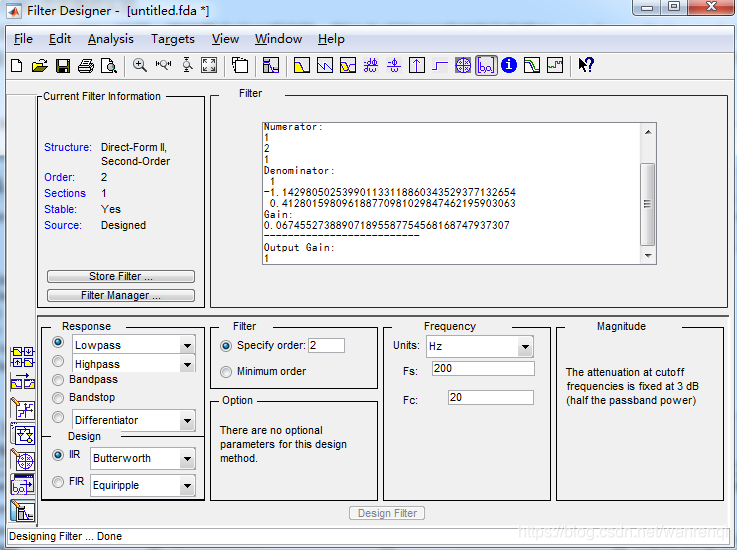

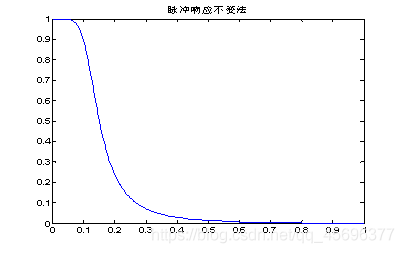

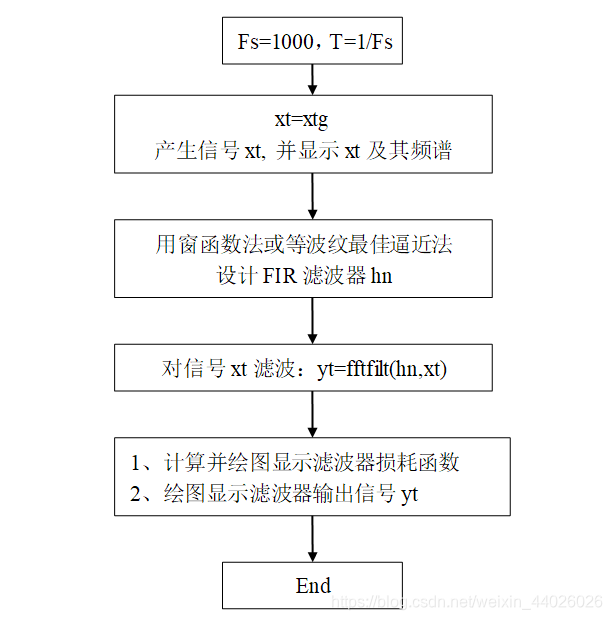

趁着这两天刚考完试,DSP忘掉的东西还不多,赶紧写篇note记录一下考试那几天总结的课本上经典数字滤波器的一般设计流程。 说实话,抛开数学上映射关系的推导不谈的话,其实基于巴特沃斯模拟滤波器来设计巴特沃斯数字...

数字验证流程概述

标签: 芯片 systemverilog 硬件工程

数字系统的设计层级(行为级、RTL、门级)1 层级介绍1.1 Behavior级1.2 RTL级 1 层级介绍 数字系统设计层级从上到下可以分为: Idea——>行为级描述——>RTL级描述——>门级网标——>物理版图 1.1 ...

数字IC设计需要学什么?

标签: fpga开发

数字电路设计:竞争冒险以及消除方法 竞争冒险 在设计数字电路过程中,往往会忽略组合逻辑中各个路径存在延迟。 (1)竞争:对于同一个模块中的同一个变量,可能会有正反输入的情况,而这两个信号来自不同的路径。 ...

数字信号处理的基本知识

数字IC设计SOC入门进阶

标签: 硬件架构

数字电路课程设计---电子钟

标签: 芯片

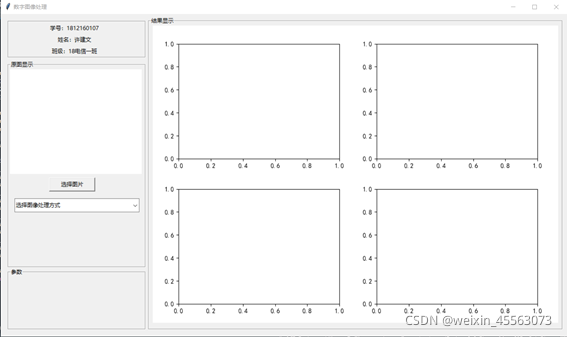

Verilog多功能数字钟的设计

推荐文章

- Python菜鸟晋级04----raw_input() 与 input()的区别_pycharm没有raw input-程序员宅基地

- 高通AR增强现实多卡识别和扩展跟踪Unity_imagetarget扩展追踪-程序员宅基地

- 对于三星手机的手工root方法-程序员宅基地

- 2021年佛山高考成绩查询,2021年高三佛山一模,看佛山高中排名-程序员宅基地

- 删除并清空应收应付模块 期初数据_应付管理系统怎么清除数据-程序员宅基地

- 嵌入式固件加密的几种方式-程序员宅基地

- 非root情况下访问手机存储位置权限的方法_不root 通讯录 存放目录-程序员宅基地

- Mybatis项目开发流程_使用mybatis的开发步骤-程序员宅基地

- 三方协议,档案,工龄,保险,户口,-程序员宅基地

- 华为交换机命令 端口速率_华为S5700交换机的端口QOS限速问题-程序员宅基地