核间通信的主要目标是:充分利用硬件提供的机制,实现高效的CORE间通信;给需要CORE间通信的应用程序提供简洁高效的编程接口。 根据所使用的硬件特性,核间通信可能的实现机制有: 1) Mailbox中断; 2) 基于共享...

”核间中断“ 的搜索结果

文章目录APIC -- 高级可编程中断控制器1.x86 中断2.Local APIC2.1.1 使能或禁止 Local APIC2.1.2 重定位 Local APIC 寄存器基地址2.2 Local APIC 寄存器2.2.1 Local APIC ID 寄存器2.2.2 Local APIC版本寄存器2.2.3 ...

中断是什么?中断的汉语解释是半中间发生阻隔、停顿或故障而断开。那么,在计算机系统中,我们为什么需要“阻隔、停顿和断开”呢?举个日常生活中的例子,比如说我正在厨房用煤气烧一壶水,这样就只能守在厨房里,...

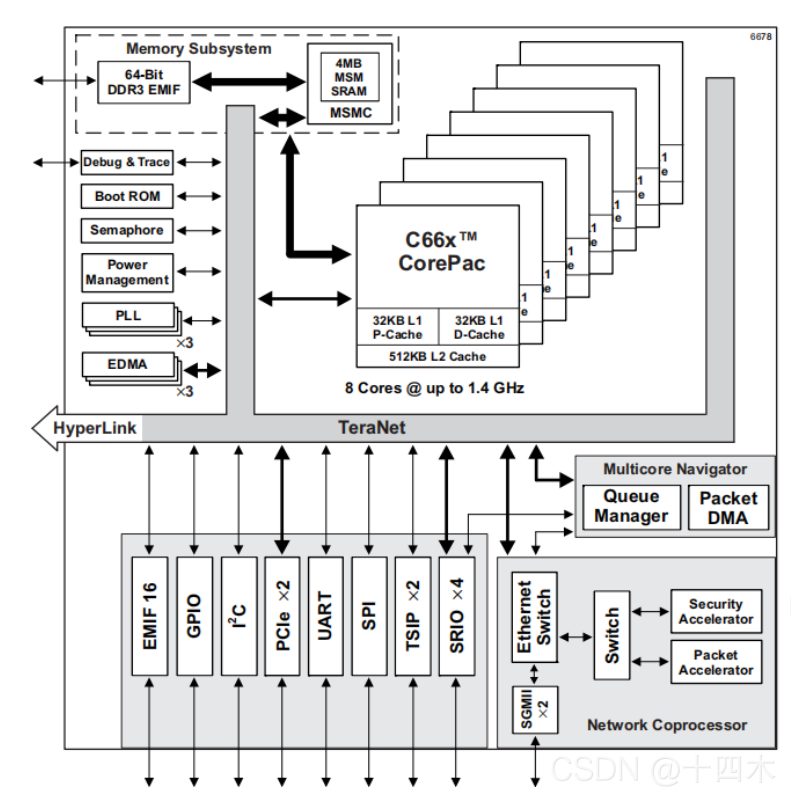

该机制将程序通信架构进行层级化设计,采用SRIO(Serial RapidIO)实现处理器间通信,通过核间中断Notify以及共享变量实现处理器内核心间通信,通过信号量实现核心内各线程间通信。为验证该机制的实用性与高效性,...

本发明实施例涉及通信技术领域,尤其涉及一种PCIe中断方法和系统。...基于引脚的PCI中断也就是INTx中断,经常在几个设备间共享,内核必须调用与该中断相关的每一个中断处理函数,效率比较低。当...

中断(Interrupt)包括中断和异常两种类型,异常通常由CPU上执行的指令直接触发,而中断是由外设发出的电信号触发的,但是那么是否所有的外设都直接接在CPU的中断PIN脚上触发中断?CPU有多少负责中断额PIN脚?CPU...

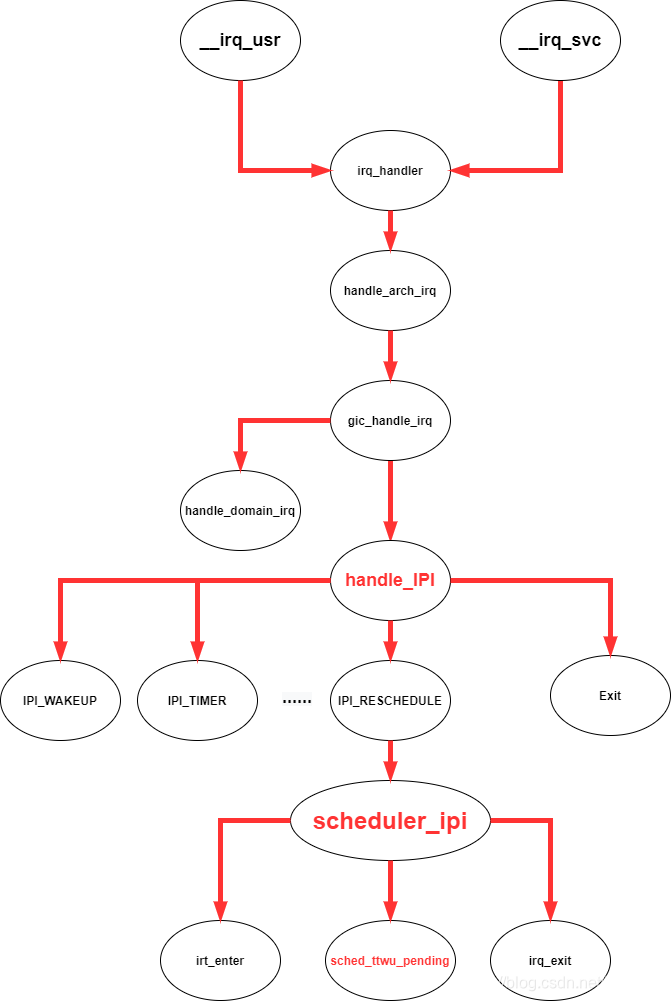

linux中断是怎么回事,看看?

MCAL多核中断配置方法

标签: autosar

关于多核ECU的中断向量表,热心网友问了一个很好的问题 今天研究了一下,先说结论: 每个core都有自己单独的memory去存储自己的中断向量表,而且每个core的中断优先级是相互独立的。也就是说,每个core都可以有...

目前,片上多核系统的设计已有一定发展,但在处理器间通信和中断方面仍需进一步的研究。本文在处理器间通信和中断控制方面进行了深入的研究。 MicroBlaze是一个被优化过的可以在Xilinx公司FPGA中运行的软核处理器...

接下来,重点介绍了核间通信的概念与几种实现方式,尤其是基于消息池的控制/状态通信。然后,对内核互斥、初始化流程等一些重要的细节展开了论述。最后提出了双核任务分工的两种应用模型,并分别举例。 背景与基本...

《英飞凌 AURIX 系列单片机的HSM详解(1)——何为HSM》 《英飞凌 AURIX 系列单片机的HSM详解(2)——与HSM...HSM核可以向主核发送中断,支持两个中断,主Tricore核中断控制寄存器地址分别为:0xF0038870u 、0xF003

本章描述了 Cortex-R52 处理器实现的通用中断控制器 (GIC)。

要想充分发挥芯片的性能,熟练掌握其中断管理系统是必不可少的。中断,作为MCU与外界交互的重要手段,能够让我们的程序实时响应外部事件,从而提高系统的整体效率和实时性。在本文中,我们将深入探讨STM32F103VET6的...

所有的事物都是依靠中断来解决问题的。计算机更是如此,依靠时钟发生器,人为的设置没几个时钟周期做一个任务,不管是否做完,一旦规定的时间到了,那么就要强制“中断”,以作下一个任务……就这样,直道所有的任务...

ZYNQ裸板:中断篇

标签: 嵌入式

推荐文章

- c语言链表查找成绩不及格,【查找链表面试题】面试问题:C语言学生成绩… - 看准网...-程序员宅基地

- 计算机网络:20 网络应用需求_应用对网络需求-程序员宅基地

- BEVFusion论文解读-程序员宅基地

- multisim怎么设置晶体管rbe_山东大学 模电实验 实验一:单极放大器 - 图文 --程序员宅基地

- 华为OD机试真题-灰度图恢复-2023年OD统一考试(C卷)-程序员宅基地

- 【机器学习】(周志华--西瓜书) 真正例率(TPR)、假正例率(FPR)与查准率(P)、查全率(R)_真正例率和假正例率,查准率,查全率,概念,区别,联系-程序员宅基地

- Python Django 版本对应表以及Mysql对应版本_django版本和mysql对应关系-程序员宅基地

- Maven的pom.xml文件结构之基本配置packaging和多模块聚合结构_pom <packaging>-程序员宅基地

- Composer 原理(二) -- 小丑_composer repositories-程序员宅基地

- W5500+F4官网TCPClient代码出现IP读取有问题,乱码问题_w5500 ping 网络助手 乱码 send(sock_tcps,tcp_server_buff,-程序员宅基地