”逻辑综合工具“ 的搜索结果

1小时玩转数字电路.rar AHB-SRAMC和FIFO的设计与验证.rar clock skew.rar IC攻城狮求职宝典.rar linux basic.rar Linux EDA虚拟机 - 个人学习IC设计.rar Perl语言在芯片设计中的应用.rar SoC芯片设计技能专题.rar ...

逻辑综合工具designCompiler使用教程

【DC与逻辑综合】逻辑综合基础

标签: 其他

逻辑综合基础知识

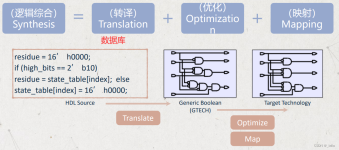

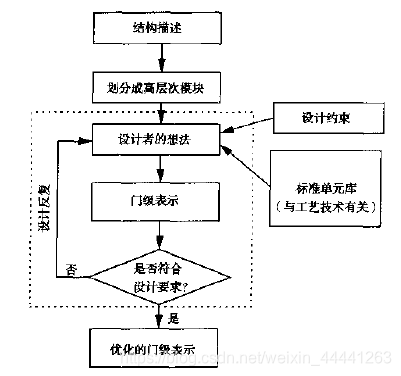

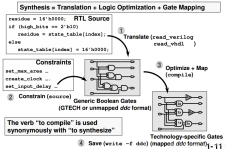

4.1 逻辑综合概述 4.1.1 逻辑综合的概念 综合(synthesis):就是把思想转换为实现欲想功能的可制造的设计。综合是约束驱动 和基于路径的。 在这里,综合也就是把行为级或 RTL 级的 HDL 描述转换为门级电路的过程,...

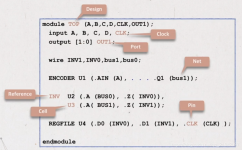

1、逻辑综合(Logic Synthesis) 将寄存器传输级(RTL,Register Transfer Level)的hdl代码转换为与工艺相关的门级网表(Gate Level Netlist)的过程 DC中的八种设计实体 设计(Design):一种能完成一定逻辑...

文章目录课程内容笔记00:00开始至 本节视频来源于DC视频教程,本节主要约束...影响输入端口逻辑部分M和输出逻辑部分S的选择。 当一条约束都不加时候,DC也能编译,不过编译出来的未必能符合工作环境。 set_load代表负

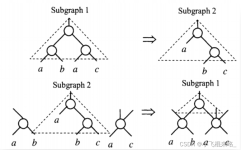

数字逻辑综合工具-DC-06 ——综合优化过程 编译的策略:Top-down (做设计有两种策略:top-down 和 bottom-up) 设计一定是一种层次化的结构,一层一层地去例化 Top-down只有一层的约束,针对某些模块,可能会有一些...

数字逻辑综合工具实践-DC-07 ——综合优化(二)和RTL coding 和DFT 主要内容: 1、 Pipeline优化 2、 RTL设计时的一些注意事项 3、 DFT简介 (DFT是后端里很重要的一步) 【流水线寄存器】 组合路径过长,timing不...

数字逻辑综合工具-DC-04 ——怎样增加时序约束(Timing Constraints) 逻辑综合的过程为:转化 优化 映射 另外还有环境约束和面积约束 时序有三个大的方面 input logic paths internal paths output paths 一个项目...

数字逻辑综合工具-DC-05 ——环境约束 环境设置通常包含以下几个方面: 1、 Input drivers和transition times(设置驱动能力、转换时间,而不是一个理想信号) 2、 Capacitive output loads(设置要驱动的电容负载)...

1.setup文件 history 查看过去执行的命令 alias 重命名 history命名为h 2.用read指令读入verilog文件 读入多个文件时,读入的首个文件默认为顶层文件,也可用连接符同时读入多个文件,首个文件默认为顶层文件。...

【分频时钟input delay】 (找短的间隔) 【多时钟output delay】 记得要用add_delay 也是找短的 【时钟之间的uncertainty】 ...模仿两个时钟之间的偏移量 要用-from -to指定两个clock(注意是get_clocks而不是...

数字逻辑综合工具-DC-08 时序分析 综合结束之后,如何确定这个网表能不能用。 【Timing Reports】 report_timing Incremental 信息包含了Net 和 Cell一起的delay (这两个延迟也可以分别报告) 【report_timing...

对于reset 和clock这种大扇出的信号来说,必须要人为设置为ideal network,不要让DC动它,因为线负载模型对于这些大扇出的情况估算不准。 如果不添加don’t ...全是ideal network的信号经过一些逻辑还是ideal的...

逻辑综合介绍

第十一课:逻辑综合基本原理及设计输入

标签: 后端

swjtu电子设计自动化(EDA)实验8报告

前端综合脚本文件,完成一个DTMF的前端综合,时钟周期为8ns

IC 流程之逻辑综合

标签: fpga开发

综合是指自动将上一个设计层次的数据转换成下一个层次的设计数据,可大大减少人工消耗,提高设计效率、准确度和复用性。本文介绍逻辑综合的基本概念和优化策略

1.1 逻辑综合 1.2 RTL综合 1.3 高级综合 2、组合逻辑的综合 2.1 优先级结构的综合 2.2 利用逻辑无关紧要条件 2.3 ASIC单元与资源共享 3.带锁存器的时序逻辑综合 3.1 锁存器的无意综合 3.2 锁存器的有意综合...

推荐文章

- Python Django 版本对应表以及Mysql对应版本_django版本和mysql对应关系-程序员宅基地

- Maven的pom.xml文件结构之基本配置packaging和多模块聚合结构_pom <packaging>-程序员宅基地

- Composer 原理(二) -- 小丑_composer repositories-程序员宅基地

- W5500+F4官网TCPClient代码出现IP读取有问题,乱码问题_w5500 ping 网络助手 乱码 send(sock_tcps,tcp_server_buff,-程序员宅基地

- Python 攻克移动开发失败!_beeware-程序员宅基地

- Swift4.0_Timer 的基本使用_swift timer 暂停-程序员宅基地

- 元素三大等待-程序员宅基地

- Java软件工程师职位分析_java岗位分析-程序员宅基地

- Java:Unreachable code的解决方法_java unreachable code-程序员宅基地

- 标签data-*自定义属性值和根据data属性值查找对应标签_如何根据data-*属性获取对应的标签对象-程序员宅基地