”高云FPGA“ 的搜索结果

https://blog.csdn.net/whik1194/article/details/127234930

https://blog.csdn.net/whik1194/article/details/127235037

FPGA作为一种逻辑芯片,硬件架构独特,具有并行性、低延时性...本篇主要介绍高云FPGA芯片和入手开发板详细介绍。高云半导体Arora Ⅴ系列FPGA产品是高云半导体晨熙®家族第五代产品。基于22nm先进工艺的可编辑逻辑器件。

本篇安装高云的开发软件Gowin,并且描述了一个基于高云fpga的程序的开发环境和完整的下载运行过程。

Gowin里面能不能直接拷贝一个管脚约束文件进去用?

项目需要做什么,了解系统的功能,如果是大型的项目还会划分模块二选一多路器,两个输入IO(a,b)可以是高电平可以是低电平,一个sel选择信号当sel为0时候输出按键1的状态当sel为1时候输出按键2的状态。

使用高云内置IP核实现多路不同时钟输出输入时钟50M由晶振提供软件开发环境高云V1.99版本硬件开发环境采用小梅哥ACG525(主芯片GW5A-LV25-UG324C2)

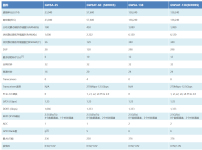

以型号为“GW5A-EV25MG196SC2/I1”的高云FPGA情况为例,该型号高云FPGA具有逻辑单元-查找表(LUT4)23040个,逻辑单元-寄存器(REG)23040个,BSRAM为1008Kb。是构成高云半导体 FPGA 产品内核的基本单元,如图2-2所...

开发板的底板原理图

国产高云FPGA:纯verilog实现视频图像缩放,提供6套GOWIN工程源码和技术支持 本文使用国产高云GW2A-LV18PG484C7/I6型号的FPGA做纯verilog实现视频图像缩放,视频源有两种,分别对应开发者手里有没有摄像头的情况,一...

https://blog.csdn.net/whik1194/article/details/127235085

开发板的底板原理图

本作品是一款基于FPGA开发设计的多功能数字时钟,在结合利用高云开发板的相关硬件资源的情况下,设计了这样的一款多功能数字时钟。该数字时钟具备有以下的相关功能: 1、具有基本走时功能,时间范围是00:00:00~23:59...

高云FPGA调试记录(一)点灯

GW1NSR-4C ARM处理器部分共有两个定时器,这两个定时器都是32位的,可以产生中断请求,也可以对外部输入信号进行计数,这两个定时器都挂载在APB1总线上,时钟源是PCLK1。

HDMI 显示实现的方案同 LVDS 一样,只是 HDMI 采用自带的 DVI TX IP 实现并行 RGB 转。硬件设计上需要注意 HDMI TX 的应用,框起来的部分需要上拉到 3.3V,LVDS 的 Bank。TMDS 协议,点亮 HDMI 接口的显示器,需要...

高云FPGA的LVDS应用

标签: fpga开发

LVDS使用原语实现LVDS的驱动,没有IP使用(官网IP参考有错误),通过PLL产生LVDS串行时钟和并行像素点时钟,采用FPGA生成RGB测试图并,通过LVDS原语转成LVDS串行差分信号,实现LVDS屏幕的点亮,参考例程提供的是点亮...

高云FPGA云源软件下载

标签: fpga开发

高云FPGA云源软件下载

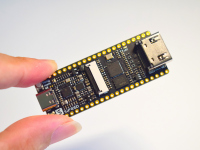

适用于高云FPGA的JTAG

标签: fpga开发

用于高云FPGA的下载器测试

【此资源可私信博主有偿获取】 Linux项目是一个开放源代码的操作系统项目,由林纳斯·托瓦兹(Linus Torvalds)于1991年首次发布。该项目以Linux内核为核心,围绕其构建了一个完整的操作系统,包括各种系统工具、库...

国产高云FPGA开发软件GOWIN的下载、安装、Licence共享,按照我的方案保证立马能用,不能用你铲我耳屎

国产高云FPGA:Gowin 在线逻辑分析仪的使用手把手教学,出不了波形你铲我耳屎

国产高云FPGA:Gowin 联合 Modelsim 仿真教程手把手教学,出不了波形你铲我耳屎

高云小蜜蜂系列FPGA系列教程

推荐文章

- 手写一个SpringMVC框架(有助于理解springMVC) 侵立删_springmvc可以用来写安卓后端吗-程序员宅基地

- 线性判别分析LDA((公式推导+举例应用))_lda推导-程序员宅基地

- C# 结构体(Struct)精讲_c# struct-程序员宅基地

- 支付宝Wap支付你了解多少?_阿里wap支付-程序员宅基地

- Java计算器编写,实现循环输入_java简易计算器可使用户多次输入-程序员宅基地

- 【多维Dij+DP】牛客小白月赛75 D-程序员宅基地

- Android之内存优化与OOM-程序员宅基地

- Azure Machine Learning - 视频AI技术_azure ai 視頻索引器-程序员宅基地

- 个人知识管理软件使用感受-程序员宅基地

- WWDC2019 ------深入理解App启动_wwdc app启动-程序员宅基地