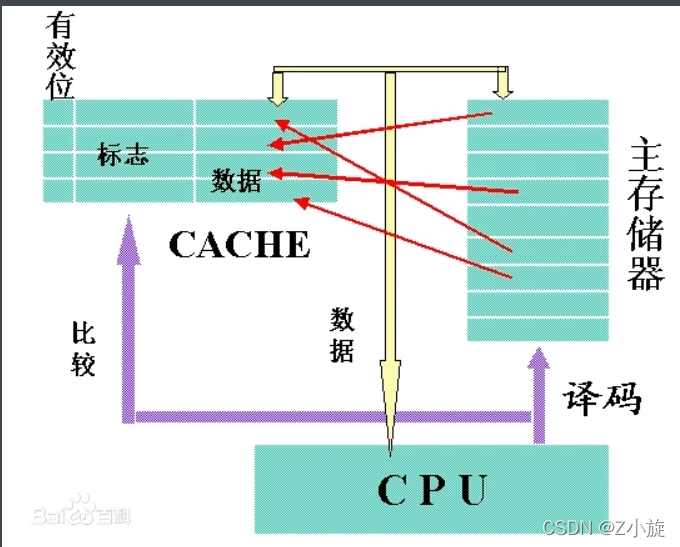

计算机中的CPU与主存之间存在速度差异,为了补偿这个差异,CPU内部增加了高速缓存。高速缓存存储了主存中的部分数据副本,CPU可以直接从高速缓存中读取数据,大大提高了读取速度。高速缓存的工作原理包括高速缓存线、非...

”高速缓存Cache“ 的搜索结果

当第一代RISC微处理器刚出现时,标准存储器元件的速度比当时微处理器的速度快。很快,半导体工艺技术的进展被用来提高微处理器的速度。标准DRAM部件虽然也快了一些,但其发展的主要精力则放在提高存储容量上。...

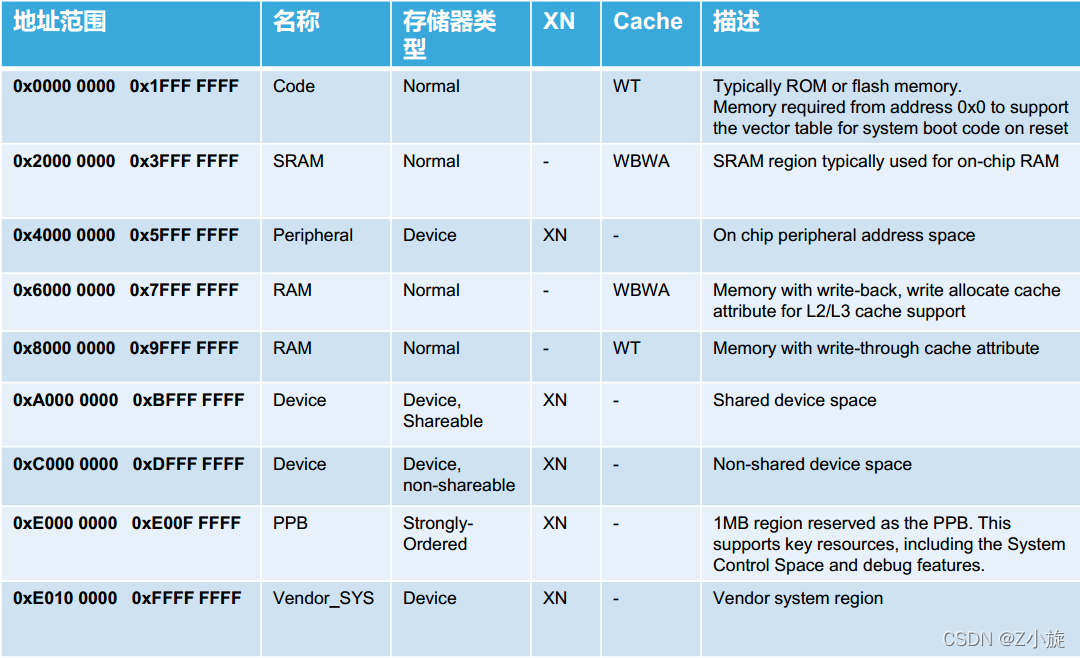

STM32F7x6培训_高速缓存 Cache

计算机缓存Cache以及Cache Line详解 - 围城的文章 - 知乎 https://zhuanlan.zhihu.com/p/37749443 L1,L2,L3 Cache究竟在哪里? - 老狼的文章 - 知乎 https://zhuanlan.zhihu.com/p/31422201 Cache是怎么组织和...

提供方法解决appscan扫描出来的漏洞《发现可高速缓存的SSL页面》,主要是设置页面不被缓存

系分 系统分析师 高速缓存 组相联 地址变换表

①程序局部性原理定义:对大量典型程序运行情况分析的结果表明,在较短时间内,程序产生的地址往往集中在存储器的一个很小的范围,这种现象称为程序访问的局部性,可细分为时间局部性和空间局部性。...

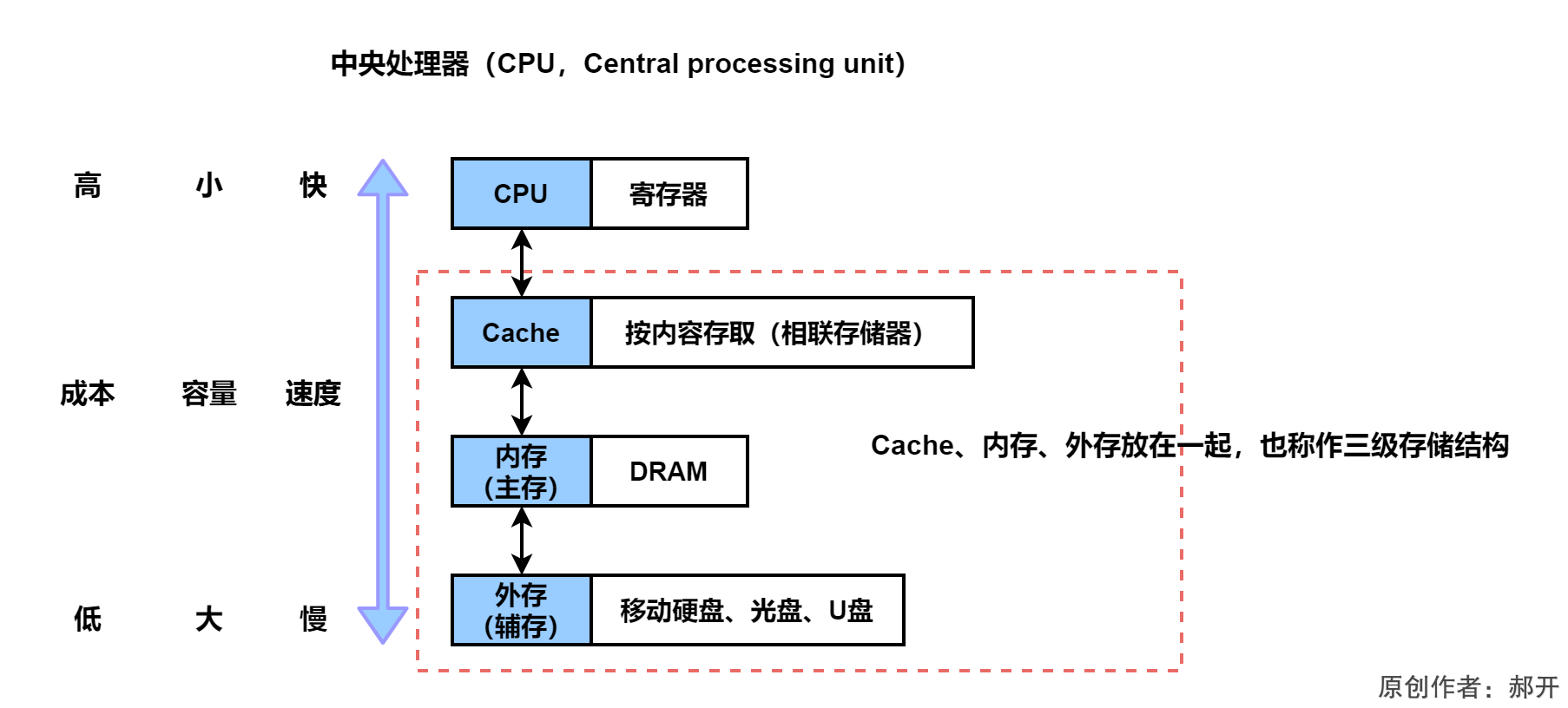

定义 高速缓冲存储器是用来存放当前最活跃... 高速缓存还解决CPU与内存速度不匹配的问题。高速缓存和CPU的速度几乎一样,其速度一般是内存的5-10倍。 其实cpu每次取指令的时候如果一个字节一个字节取,效率就比较

高速缓存Cache的映射方式

标签: 操作系统

简单来说,就是整个Cache,映射到主存中,是一个主存块组(n个连续主存块为一组) 地址划分:主存组号,Cache行数,块内地址(按顺序排列的) 主存组号:主存块号从0开始,顺序,每n块为一组,从第0组开始 Cache行数...

高速缓存cache cache的基本原理 cache是一种小容量高速缓冲存储器,由快速SRAM组成。在CPU和贮存之间设置cache,总是把主存中被频繁访问的活跃程序块和数据块复制到cache。 cache是为了解决CPU与主存的...

c++实现高速缓存Cache

【代码】CPU高速缓存cache分类与查看。

高速缓存Cache与主存间采用全相联的地址影像方式,高速缓存的容量为4MB(2006)● 高速缓存Cache与主存间采用全相联的地址影像方式,高速缓存的容量为4MB,分为4块,每块1MB,主存容量为256MB,若主存读写时间为30ns,...

高速缓存(cache) 概念和原理 cache基本思想 ▪ cache 存储器( Cache memories ) ▪ 在处理器附近增加一个小容量快速存储器(cache) ▪ 基于SRAM,由硬件自动管理 cache基本思想: ▪ 频繁访问的数据块存储在cache中 ...

高速缓存cache1

标签: 操作系统

首先,计算机中主要有3种存储设备,磁盘,主存,寄存器。 计算机要运行程序,得让处理器cpu去访问存储设备,所以如何让处理器...从而有了高速缓存存储器cache,它是一种存储大小与读取速度均介于主存和寄存器之间的存

存储器的组织形式: 数据总是在相邻两层之间复制传送,最小传送单位是定长块,互为副本(不删除) ⭐️指令和数据有时间局部性和空间局部...CPU往往需要重复读取同样的数据块, Cache的引入与缓存容量的增大,可...

介绍了 Cache 的多路组相联,以及 Cache 的性能、一次性设计。

推荐文章

- 大数据基础hadoop / hive / hbase_hadoop、hbase、hive 原理-程序员宅基地

- Shiro与Spring结合时报Configuration error: No realms have been configured! One or more realms must be……_configuration error: no realms have been configure-程序员宅基地

- 疟原虫感染治疗癌症,灵感竟然来源于地图-程序员宅基地

- PAT乙级C语言1005 继续(3n+1)思想_pat1005继续 c语言-程序员宅基地

- 【啃书】《智能优化算法及其MATLAB实例》例5.1蚁群算法求解TSP问题_蚁群算法 约束优化 matlab-程序员宅基地

- WPF页面切换之Page与Window_wpf window page-程序员宅基地

- C++抽象数据类型(ADT)表示和实现--链队列(Queue)_c++数据结构adt怎么写-程序员宅基地

- 空调采集网关让空调更智能,让节能更简单!_空调外接网关进行数据采集的方案-程序员宅基地

- 经典收藏 50个jQuery Mobile开发技巧集萃-程序员宅基地

- C++GDI做进度条-程序员宅基地