其次,由于FPGA中实现2分频电路的延迟相对较大,因此需要对输入信号做好时序分析和优化工作,以确保2分频电路的正确运行。最后,在FPGA开发中,我们也可以使用Verilog语言实现其他电路逻辑,例如4分频、8分频等等。

”FPGA二分频代码“ 的搜索结果

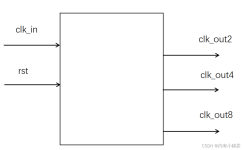

将原始时钟分为2分频、4分频、8分频、3分频,以及2hz分频。即将原始时钟周期分别2倍、4倍、8倍、3倍,本次例程尝试了例化调用,将各种分频单独写成小模块。 代码设计 1、顶层代码 module Clk_Divider# //模块名 Clk_...

Quarteus下用Verilog所写的二分频代码。内含激励文件 亲测可用,用meldusim可以查看波形图

VerilogHDL二分频代码 ①二分频代码 module FP2( input clk, output reg clk_s ); initial clk_s <= 1'b0; //初始化 always @(posedge clk) //时钟上升沿敏感 begin if(clk == 1'b1) //当时钟为高电平 .....

FPGA分频器是一种常用于数字信号处理、通信系统、雷达系统等领域的电路,其作用是将信号时钟分成多个频频率。分频电路是数字电路中常见的...本文将详细介绍FPGA分频器的设计方法,并附上Verilog代码示例,以供参考。

一开始我觉得会比较困难,因为要设计D触发器,然后再利用D触发器去做二分频,在看了大家的博客设计完D触发器后,我发现!!!

在数字电路中,频率是至关重要的。当我们需要改变频率时,最常见的方法是使用分...比如说,如果我们需要将输入时钟信号分频为原来的一半,那么。接下来,我们需要设计一个分频器,在 SystemVerilog 中,我们可以使用。

继续更新,万一用户将分频系数设为0怎么办...采用 4 个开关以二进制形式设定分频系数(1-10),实现对已知信号的分频。(关于VHDL中的buffer,我以后还需要查阅专业资料进一步学习)需要重做以便将来应对更大的分频系数。

FPGA中的时钟管理与分频技术

标签: 硬件开发

## FPGA的时钟管理与分频技术的重要性 在电子系统中,时钟信号在各个模块之间起着同步和调度的作用。而在FPGA(Field Programmable Gate Array,现场可编程门阵列)这样的可编程逻辑器件中,时钟管理与分频技术的...

总之,二分频是FPGA设计中常用的技术,可以有效地将时钟周期加倍,从而提高数字系统的性能。Verilog和SystemVerilog都提供了简便的方法来实现二分频,可以根据具体的应用场景选择适合的方法来实现。此代码使用always...

这里的时钟相当于系统时钟的6降频,两个时钟的上升沿之间为一个降频后的一个时钟周期,只不过高低电平的占空比不同。第二种方法实现(使用脉冲信号--推荐使用,与定时器的脉冲信号类似)

为了避免每次SPI驱动重写,直接参数化,尽量一劳永逸...SPI slave有什么用呢,当外部主机(cpu)要读取FPGA内部寄存器值,那就很有用了,FPGA寄存器就相当于RAM,cpu通过SPI寻址读写数据。代码仅供参考,勿做商业用途。

我们在学习FPGA的实验中可以知道我们的时钟频率只有引脚10,很多实验现象在该时钟频率下完全看不到现象,本来应该有的流水灯似的显示却变成了全亮...我们先来了解一下二分频 直接上图吧,更好理解 二分频电路图 其...

本文将介绍如何使用Verilog和VHDL编写一个实现二分频功能的FPGA设计,并提供相应的源代码。通过以上的Verilog和VHDL代码,我们可以在FPGA上实现一个简单的二分频功能。总结起来,Verilog和VHDL是两种常见的FPGA设计...

本文将介绍如何使用Verilog和VHDL编写一个实现二分频功能的FPGA设计,并提供相应的源代码。通过以上的Verilog和VHDL代码,我们可以在FPGA上实现一个简单的二分频功能。总结起来,Verilog和VHDL是两种常见的FPGA设计...

verlog yyds

分频器的练习就是计数器的一个应用分支,用设立来检验自己对计数器的使用使用熟练。真实上板代码,都是使用IP核来进行的。清零条件递增条件核心思想:明白如何使用计数器来实现特定的功能,

Verilog HDL实现奇偶分频器,二分频与三分频,Vivado仿真。

Quarteus下用Verilog所写的二分频代码。内含激励文件 亲测可用,用meldusim可以查看波形图 相关下载链接://download.csdn.net/download/kd1821035453/13120560?utm_source=bbsseo

博客已迁至[马春杰杰]http://www.machunjie.com/hardware/82.html 请移步新博客,谢谢。!

module cy4( input ext_clk_25m, //外部输入25MHz时钟信号 input ext_rst_n, //外部输入复位信号,低电平有效 output reg clk_12m5 //二分频时钟信号 ); always @(posedge ext_clk_25m ...

2.3 verilog语言编写二分频 2.3.1 本节目录 1)本节目录; 2)FPGA简介; 3)verilog简介; 4)verilog语言编写二分频; 5)本节结束。 2.3.2 FPGA简介 FPGA(Field Programmable Gate Array)是在PAL、GAL...

二分频是一种常见的时钟分频技术,即将一个时钟信号分频为原来的一半。在Vivado中,我们可以使用HDL语言(如Verilog或VHDL)来实现二分频功能。 首先,我们需要在Vivado中创建一个新的工程,并选择我们要使用的...

为了实现二分频,我们需要将每两个时钟周期划分为一个新的时钟周期,即将原始时钟信号的频率减半。在数字系统设计中,需要对时钟信号进行分频,以便将频率降低到所需的范围。该电路可以通过将输入时钟信号连接到FPGA...

我们这次来讲解使用VHDL语言编写三种不同的分频方法 代码如下: 第一种: library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_arith.all; use ieee.std_logic_unsigned.all; entity devide5m is port...

基于FPGA的分频设计1.偶数倍分频 偶数倍分频器的实现非常简单,只需要一个计数器进行计数就能实现。如需要N分频器(N为偶数),就可以由待分频的时钟触发计数器进行计数,当计数器从0计数到N/2-1时,将输出时钟进行...

推荐文章

- centos7初始化mysql 5.7.9(源码安装)-程序员宅基地

- undefined reference to `cvHaarDetectObjects'()(人脸检测)_cvhaardetectobjects未定义-程序员宅基地

- 如何将参数传递给批处理文件?_批处理 传递参数-程序员宅基地

- C++的一些小总结 类 静态成员变量/函数 this指针_c++ class 静态指针函数-程序员宅基地

- springboot小区物业管理系统7ffeo[独有源码]如何选择高质量的计算机毕业设计_小区物业管理系统er图-程序员宅基地

- mac-gradle的安装和配置,掌握这些知识点再也不怕面试通不过_mac gradle配置-程序员宅基地

- 2032:【例4.18】分解质因数(信奥一本通)-程序员宅基地

- html怎么设置默认状态,网页中如何设置默认图片?方式介绍-程序员宅基地

- milp的matlab的案例代码_matlab30个案例分析案例5代码-程序员宅基地

- html实现/ 简约好看、美观大方的个人导航页源码/开源个人主页html源码_个人导航html-程序员宅基地